# Analog IC design - the obsolete book

Ricardo Erckert

# December 2022

# Contents

| 1 | Pref     | re                                               | 9        |

|---|----------|--------------------------------------------------|----------|

| - | 1.1      | Using the book                                   | 9        |

|   | 1.2      | If you find mistakes                             | 9        |

|   | 1.3      |                                                  | 9        |

|   | 1.4      |                                                  | 10       |

|   |          |                                                  |          |

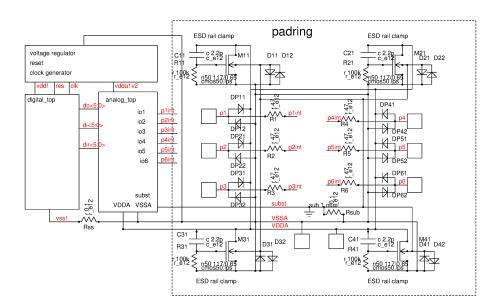

| 2 | The      | top level of a chip                              | 10       |

|   | 2.1      | How to get the correct data of a chip            | 10       |

|   |          | 2.1.1 Versioning tools                           | 10       |

|   | 2.2      | System on a chip                                 | 13       |

|   |          | 2.2.1 Where exactly is "ground"?                 | 13       |

|   |          | 2.2.2 Signals: If anything can go wrong it will! | 14       |

|   |          | 2.2.3 Timings                                    | 16       |

|   | 2.3      |                                                  | 16       |

|   | 2.4      | Hierarchy of the chip                            | 17       |

|   |          | 2.4.1 Analog on top                              | 17       |

|   | 2.5      | Down at the bottom                               | 18       |

|   |          | 2.5.1 Electric                                   | 18       |

|   |          |                                                  | 19       |

|   |          |                                                  |          |

| 3 |          |                                                  | 20       |

|   | 3.1      | - · · · · · · · · · · · · · · · · · · ·          | 22       |

|   |          |                                                  | 22       |

|   |          |                                                  | 23       |

|   |          |                                                  | 24       |

|   |          |                                                  | 24       |

|   |          | 65                                               | 25       |

|   |          |                                                  | 28       |

|   | 3.2      |                                                  | 28       |

|   |          |                                                  | 28       |

|   |          |                                                  | 29       |

|   |          |                                                  | 30       |

|   |          |                                                  | 31       |

|   |          | 3.2.5 State of the art (2020) digital processes  |          |

|   |          | 3.2.6 Programmable chips                         | 31       |

|   | <b>C</b> |                                                  |          |

| 4 |          |                                                  | 33       |

|   | 4.1      | Wires   4.1.1   Electromigration                 | 33<br>33 |

|   |          | 6                                                | зз<br>34 |

|   |          |                                                  | 35<br>35 |

|   |          |                                                  |          |

|   |          |                                                  | 36       |

|   | 4.0      | 0                                                | 37       |

|   | 4.2      |                                                  | 40       |

|   |          |                                                  | 41       |

|   |          | 6 · · · · · · · · · · · · · · · · · · ·          | 41       |

|   | 12       |                                                  | 41       |

|   | 4.3      |                                                  | 42       |

|   |          | 5                                                | 42<br>43 |

|   |          | 4.3.2 Thermal Noise of a resistors               | 43       |

|   |      | 4.3.3    | Poly silicon resistor aging:                                                                                   | 13       |

|---|------|----------|----------------------------------------------------------------------------------------------------------------|----------|

|   |      | 4.3.4    | Resistor matching                                                                                              | 14       |

|   |      | 4.3.5    | Diffused resistors                                                                                             | 14       |

|   | 4.4  | Capacito | prs                                                                                                            | 14       |

|   |      | 4.4.1    | Junction capacitors                                                                                            | 45       |

|   |      | 4.4.2    | Poly silicon capacitors                                                                                        | 46       |

|   |      | 4.4.3    | solated poly silicon capacitors                                                                                | 46       |

|   |      |          |                                                                                                                | 46       |

|   |      |          |                                                                                                                | 48       |

|   |      |          |                                                                                                                | 48       |

|   |      |          |                                                                                                                | 48       |

|   |      |          |                                                                                                                | 48       |

|   |      |          | <b>o</b> 1                                                                                                     | +0<br>49 |

|   | 4.5  |          | I                                                                                                              | +9<br>50 |

|   | 4.5  |          |                                                                                                                |          |

|   |      |          |                                                                                                                | 51       |

|   |      |          |                                                                                                                | 53       |

|   |      |          |                                                                                                                | 53       |

|   |      |          |                                                                                                                | 54       |

|   | 4.6  |          |                                                                                                                | 54       |

|   |      |          |                                                                                                                | 54       |

|   |      |          |                                                                                                                | 54       |

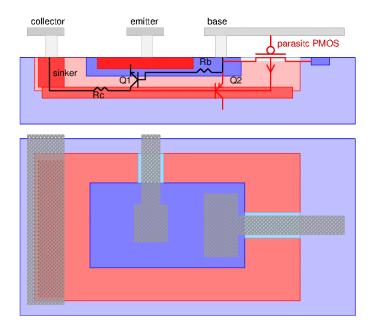

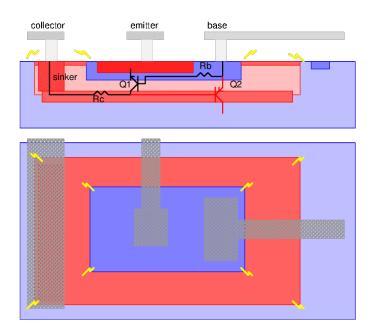

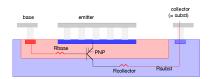

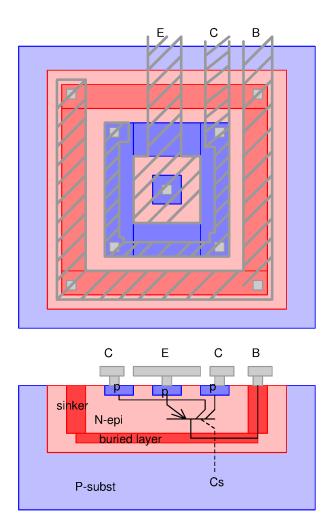

|   | 4.7  | Bipolar  | transistors and diodes                                                                                         | 55       |

|   |      | 4.7.1    | Bipolar Diodes                                                                                                 | 65       |

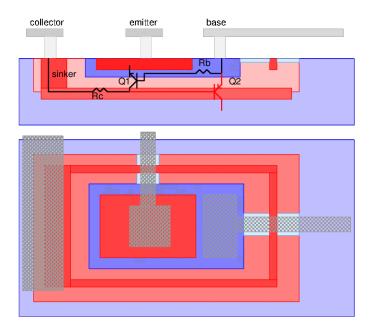

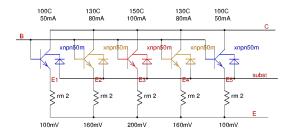

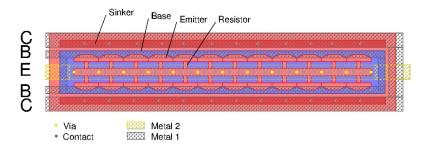

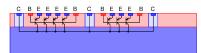

|   |      | 4.7.2    | Vertical NPN transistors                                                                                       | 59       |

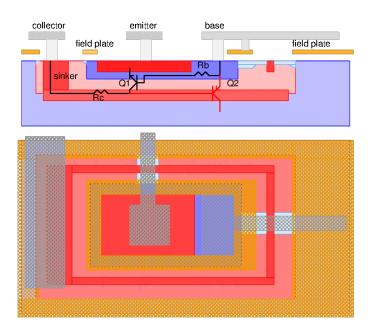

|   |      | 4.7.3    | High Voltage NPN transistors                                                                                   | 71       |

|   |      |          | • •                                                                                                            | 74       |

|   |      |          | •                                                                                                              | 74       |

|   |      |          |                                                                                                                | 76       |

|   |      |          |                                                                                                                | 76       |

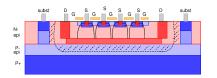

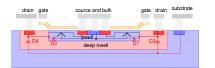

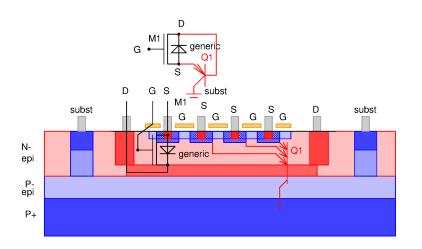

|   | 4.8  |          |                                                                                                                | 77       |

|   | 4.0  | •        |                                                                                                                | 78       |

|   |      |          |                                                                                                                | 79       |

|   |      |          |                                                                                                                | 79<br>79 |

|   |      |          |                                                                                                                | 79<br>79 |

|   |      |          | I                                                                                                              |          |

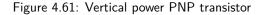

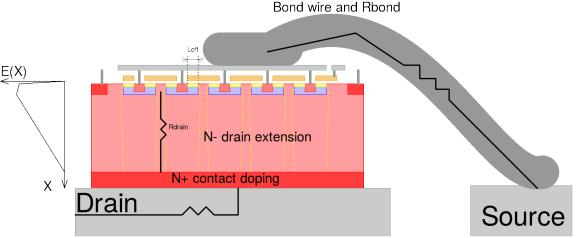

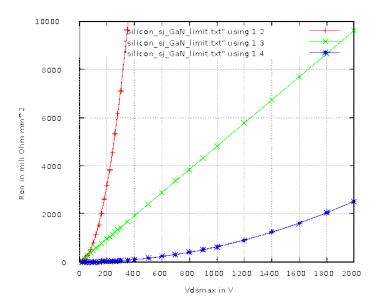

|   |      |          | Substrate power DMOS                                                                                           |          |

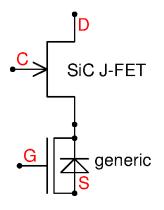

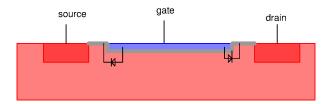

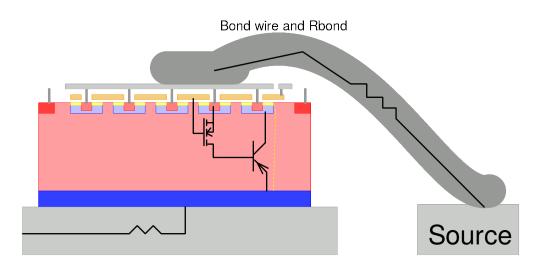

|   |      |          | SiC transistors                                                                                                |          |

|   |      |          | GaN transistors                                                                                                |          |

|   |      |          | GBT (Isolated gate bipolar transistor)                                                                         |          |

|   |      |          | <b>j</b>                                                                                                       | 36       |

|   |      | 4.8.10   |                                                                                                                | 88       |

|   |      | 4.8.11   | Photo diodes                                                                                                   | 39       |

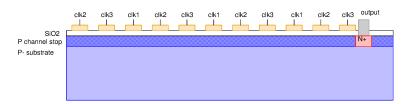

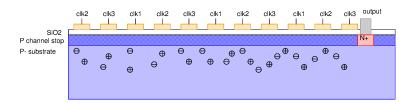

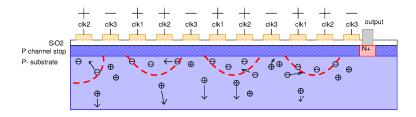

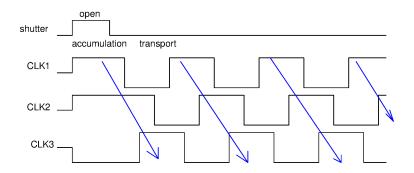

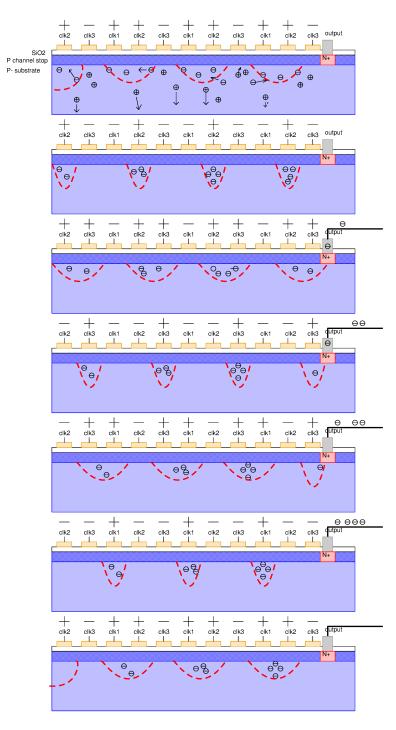

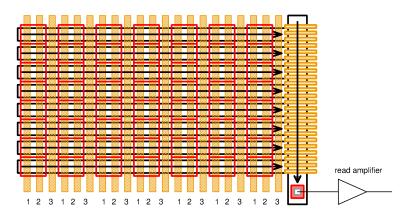

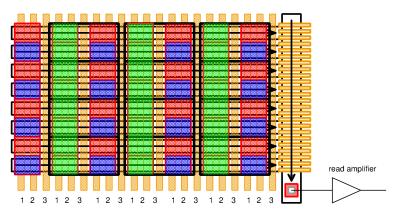

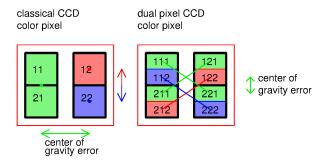

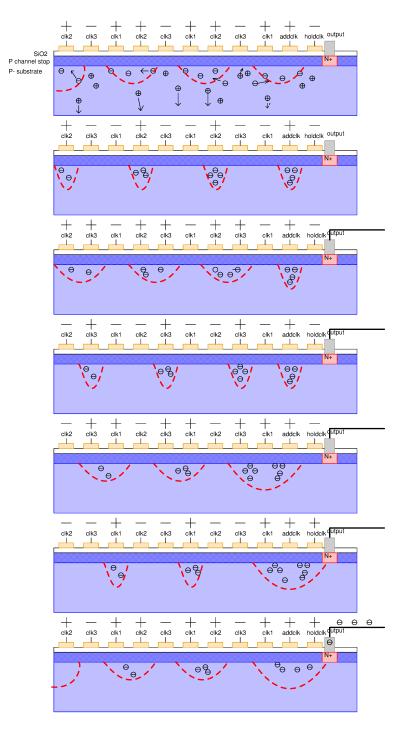

|   |      | 4.8.12   | CCD image sensors                                                                                              | 90       |

|   |      | 4.8.13   | Single Photon Avalanche Device                                                                                 | 95       |

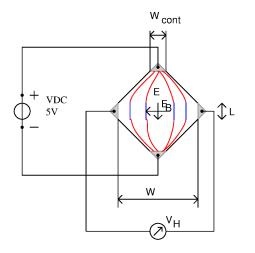

|   | 4.9  | HAL ser  | Isors                                                                                                          | 96       |

|   | 4.10 | General  | problems of high voltage components                                                                            | 97       |

|   |      | 4.10.1   | Single event burnout                                                                                           | 97       |

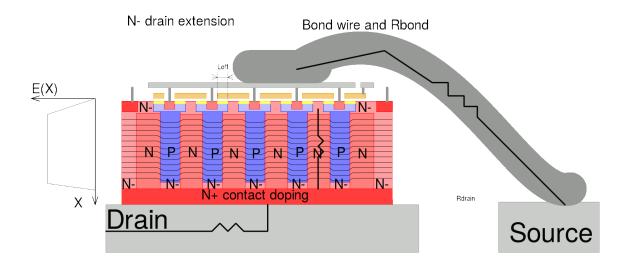

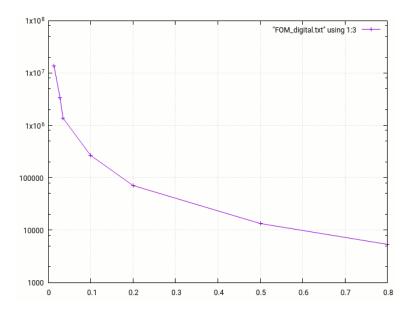

|   | 4.11 | Figure o | f Merit of a technology                                                                                        | 97       |

|   |      | -        | ••                                                                                                             | 97       |

|   |      |          |                                                                                                                |          |

| 5 | Para | sitic Co | nponents 10                                                                                                    | )0       |

|   | 5.1  | Passive  | Parasitics                                                                                                     | )0       |

|   |      | 5.1.1    | Parasitic Capacities $\ldots$ | )0       |

|   |      |          | Parasitic Inductances                                                                                          |          |

|   | 5.2  |          | Parasitics                                                                                                     |          |

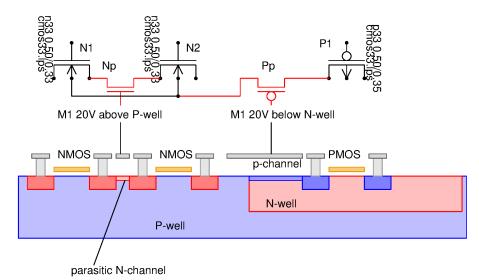

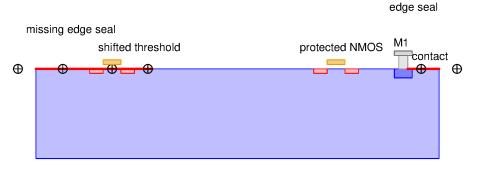

|   |      |          | Parasitic metal gate MOS transistors                                                                           |          |

|   |      |          | Accumulation of ionic contamination (BTI and NBTI)                                                             |          |

|   | 5.3  |          | rasitics                                                                                                       |          |

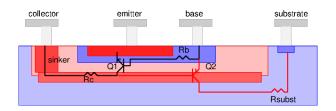

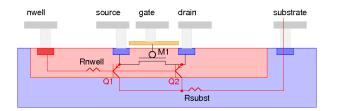

|   | J.J  |          | Parasitic substrate PNP                                                                                        |          |

|   |      |          |                                                                                                                |          |

|   |      |          | Parasitic lateral PNP transistors                                                                              |          |

|   |      |          | Parasitic lateral NPN                                                                                          |          |

|   |      |          | Parasitic vertical NPN                                                                                         |          |

|   |      |          | Substrate resistance                                                                                           |          |

|   |      | 5.3.6    | Nell resistance                                                                                                | 78       |

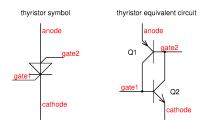

|   |     | 5.3.7    | Thyristors                                                                                |

|---|-----|----------|-------------------------------------------------------------------------------------------|

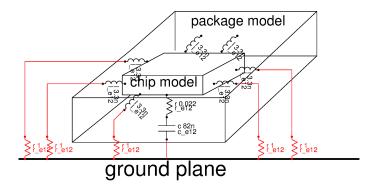

|   | 5.4 | Packag   | ge Parasitics                                                                             |

|   |     | 5.4.1    | Bond wire resistance                                                                      |

|   |     | 5.4.2    | Bond wire inductance                                                                      |

|   |     | 5.4.3    | Pin capacities                                                                            |

|   |     | 5.4.4    | Pin Inductance                                                                            |

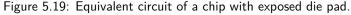

|   |     | 5.4.5    | Die pad capacity                                                                          |

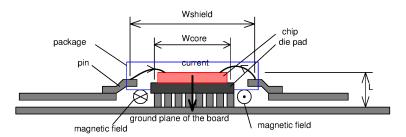

|   |     | 5.4.6    | Exposed die pad inductance and substrate inductance                                       |

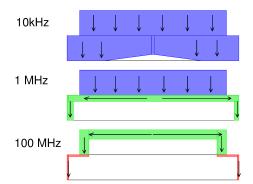

|   |     | 5.4.7    | Exposed die pad and substrate resistivity change at high frequency due to skin effect 116 |

|   |     | 5.4.8    | Charge transport in mold material                                                         |

|   |     |          |                                                                                           |

| 6 |     | ulation  | 117                                                                                       |

|   | 6.1 |          | simulation                                                                                |

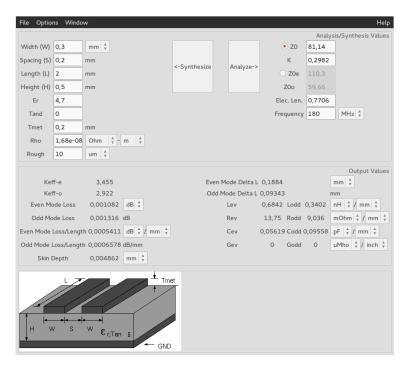

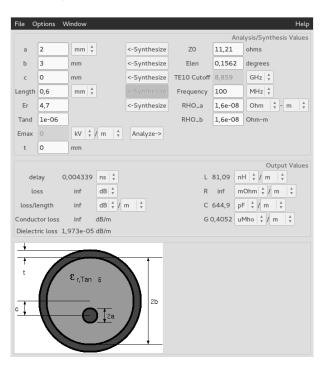

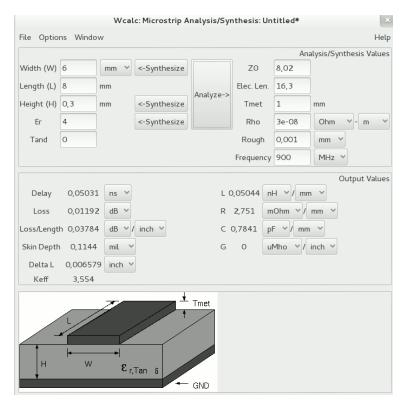

|   |     | 6.1.1    | wcalc                                                                                     |

|   |     | 6.1.2    | Fasthenry                                                                                 |

|   | 6.2 |          | tor level analog simulation                                                               |

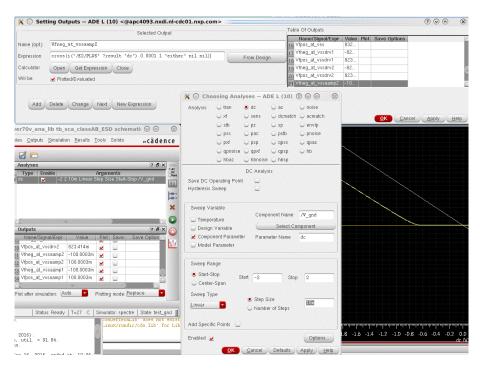

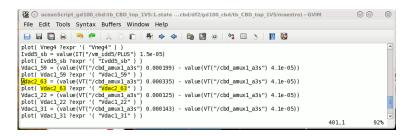

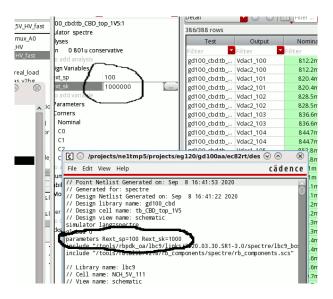

|   |     | 6.2.1    | ADE L                                                                                     |

|   |     | 6.2.2    | ADE XL                                                                                    |

|   |     | 6.2.3    | Avenue                                                                                    |

|   |     | 6.2.4    | ELDO                                                                                      |

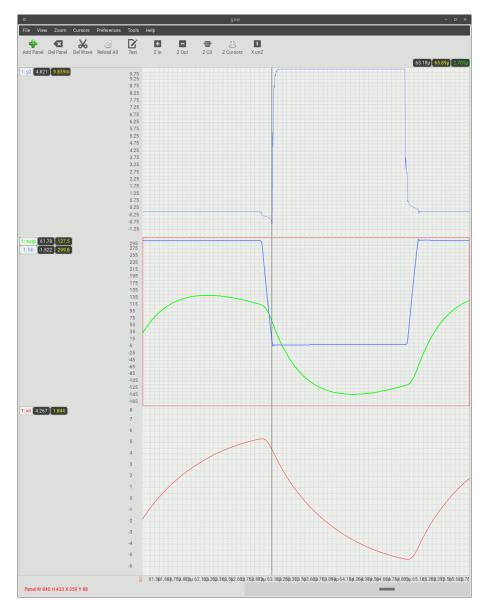

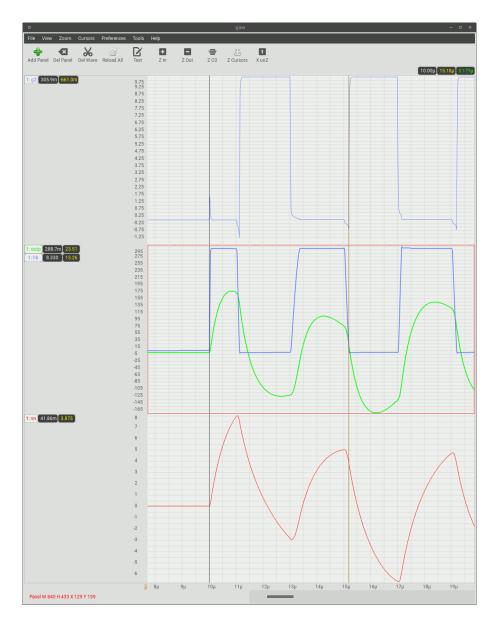

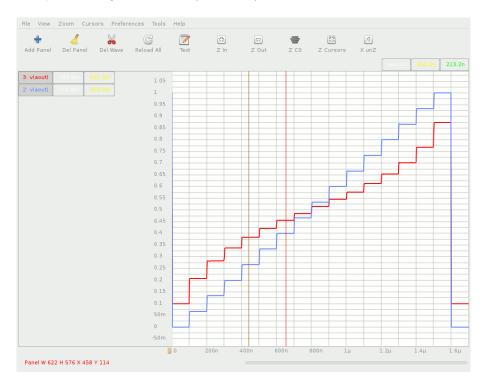

|   |     | 6.2.5    | gaw                                                                                       |

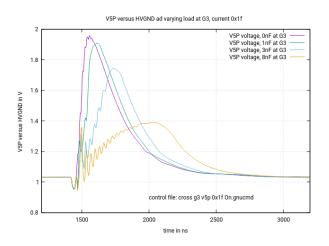

|   |     | 6.2.6    | GNUCAP                                                                                    |

|   |     | 6.2.7    | Mica and Descover                                                                         |

|   |     | 6.2.8    | Maestro                                                                                   |

|   |     | 6.2.9    | Powermill, Timemill                                                                       |

|   |     |          | SABER                                                                                     |

|   |     |          | SPECTRE                                                                                   |

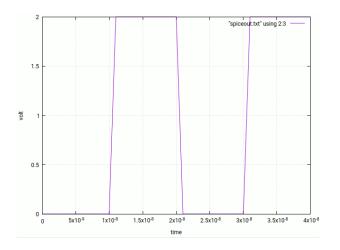

|   |     |          | SPICE                                                                                     |

|   |     |          | TITAN                                                                                     |

|   |     |          | wv                                                                                        |

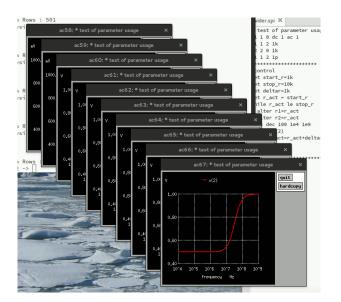

|   | 6.3 | -        | simulation                                                                                |

|   |     | 6.3.1    | Verilog and iverilog                                                                      |

|   | - · | 6.3.2    | VHDL and ghdl                                                                             |

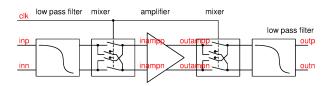

|   | 6.4 |          | signal simulation                                                                         |

|   |     | 6.4.1    | Config view                                                                               |

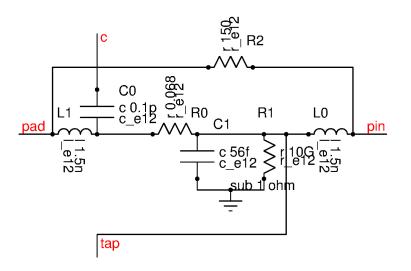

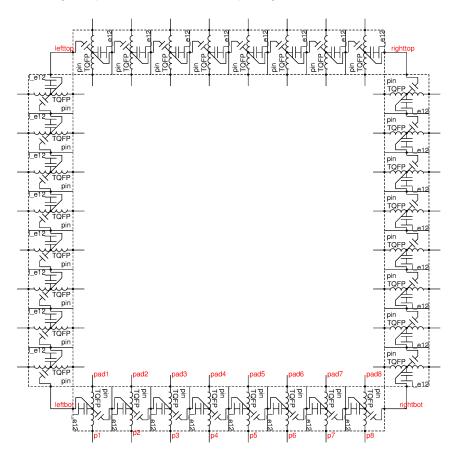

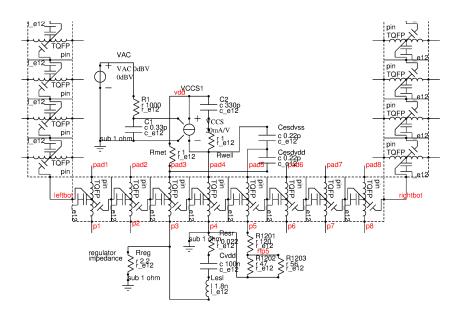

|   |     | 6.4.2    | Interface elements                                                                        |

|   |     | 6.4.3    | Simulator usage                                                                           |

|   |     | 6.4.4    | Company specific tools                                                                    |

|   |     | 6.4.5    | The checkout problem                                                                      |

|   | 6.5 | 5        | n simulation                                                                              |

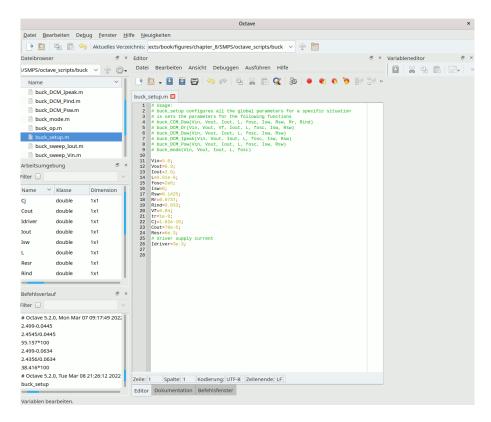

|   |     | 6.5.1    | Mathlab and Octave                                                                        |

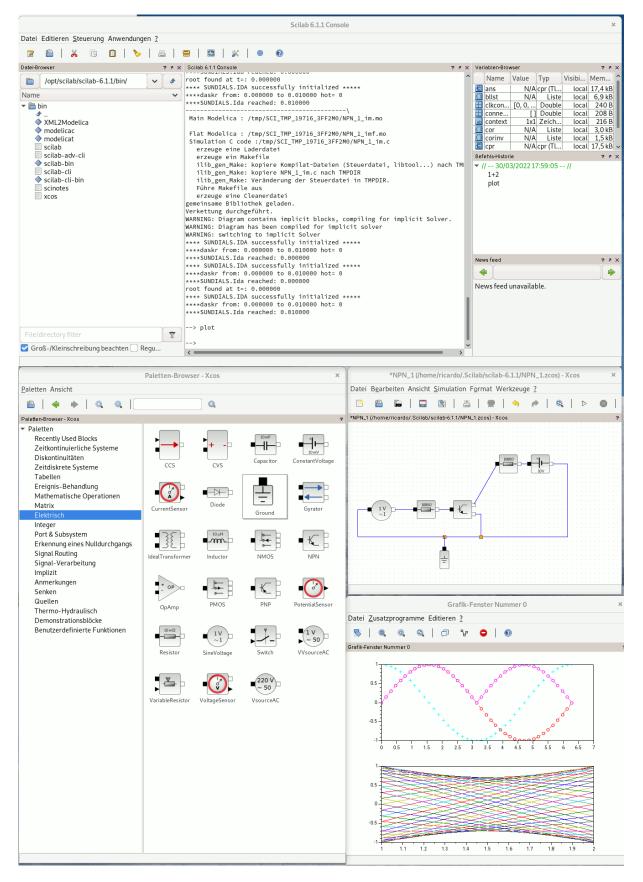

|   |     | 6.5.2    | Scilab                                                                                    |

|   |     | 6.5.3    | Jupyter                                                                                   |

|   |     | 6.5.4    | Behavioral simulation using analog simulators                                             |

|   |     | 6.5.5    | RF emission (EMC) simulation                                                              |

|   |     | 6.5.6    | Thermal simulation                                                                        |

|   |     | 6.5.7    | Using digital simulators for system simulation                                            |

|   | 6.6 | -        | ical solvers                                                                              |

|   | 6.7 |          | prm viewers                                                                               |

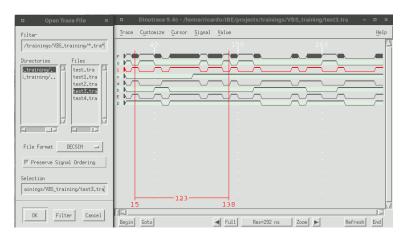

|   |     | 6.7.1    | dinotrace                                                                                 |

|   |     | 6.7.2    | gaw                                                                                       |

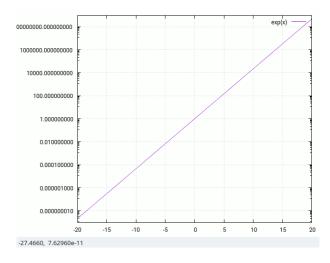

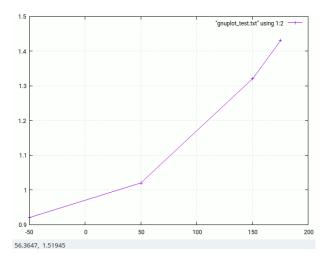

|   |     | 6.7.3    | gnuplot                                                                                   |

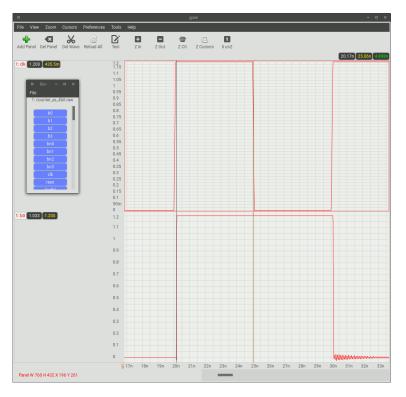

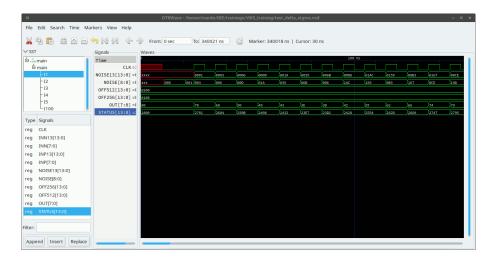

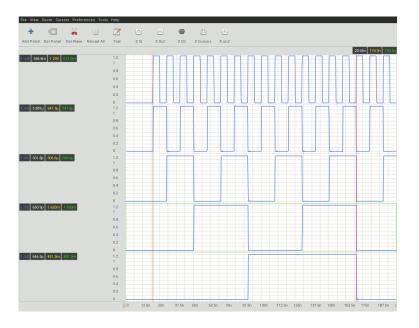

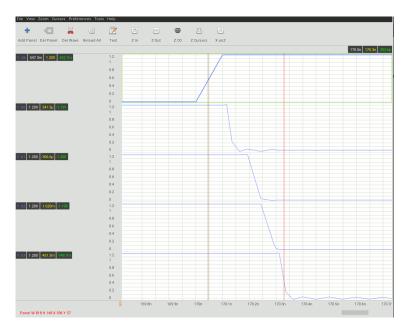

|   |     | 6.7.4    | gtkwave                                                                                   |

| 7 | D'  | - Circle | ite 163                                                                                   |

| 7 |     |          |                                                                                           |

|   | 7.1 | -        | e dividers                                                                                |

|   | 7 0 | 7.1.1    | Design for good matching                                                                  |

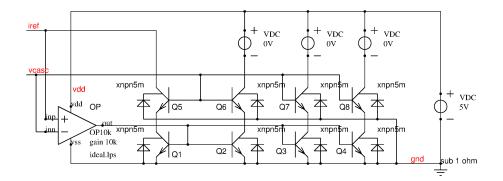

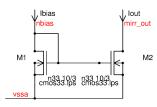

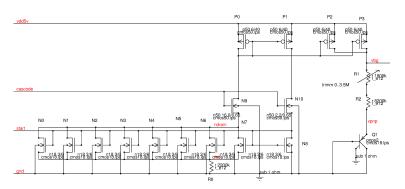

|   | 7.2 |          | t mirrors                                                                                 |

|   |     | 7.2.1    | Bipolar current mirrors                                                                   |

|   |     | 7.2.2    | MOS current mirrors                                                                       |

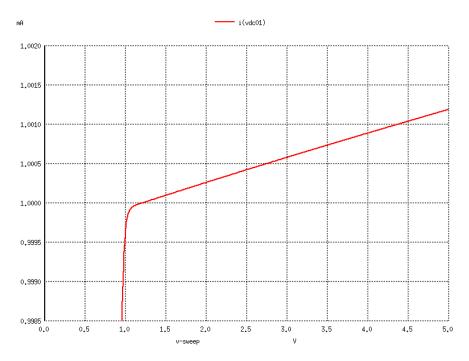

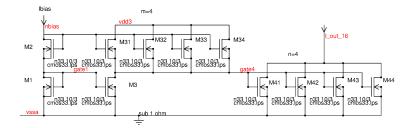

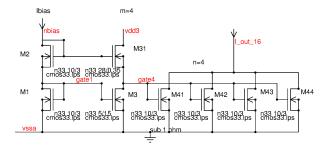

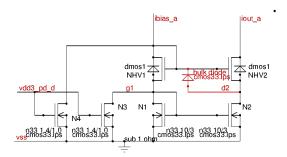

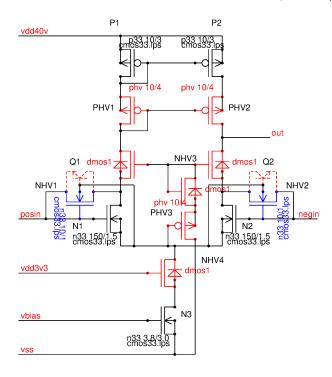

|   |     | 7.2.3    | High voltage current mirrors                                                              |

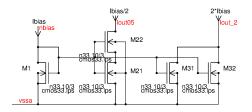

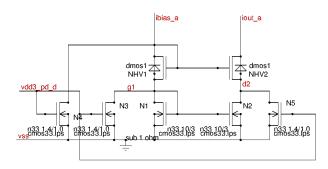

|   | 7 0 | 7.2.4    | MOS current mirrors with gm degradation                                                   |

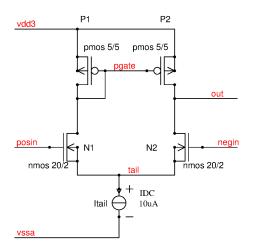

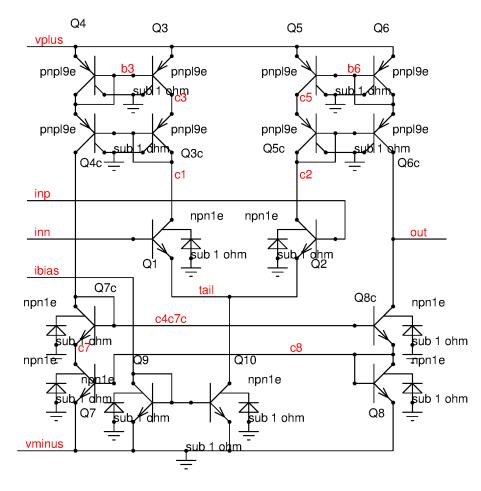

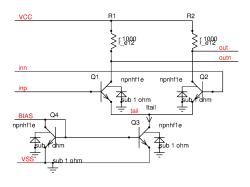

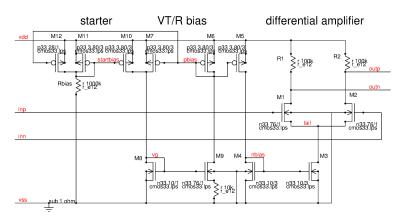

|   | 7.3 | Differe  | ntial amplifier                                                                           |

|      |         | Input protection circuits                                       |

|------|---------|-----------------------------------------------------------------|

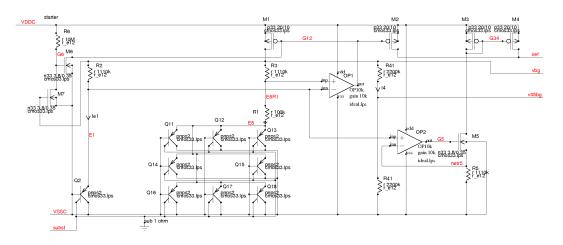

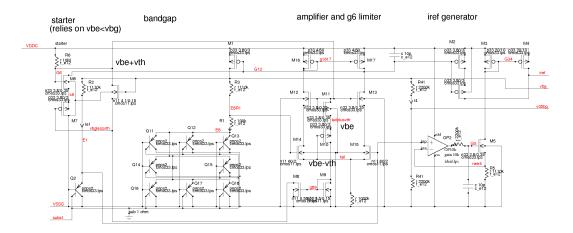

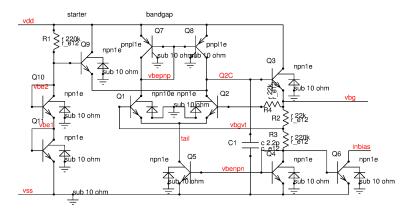

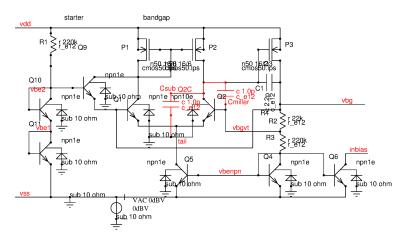

| 7.4  | Bandga  | ap circuits                                                     |

|      | 7.4.1   | The Widlar bandgap                                              |

|      | 7.4.2   | The Brokaw Bandgap                                              |

|      | 7.4.3   | The Barba CMOS bandgap                                          |

|      | 7.4.4   | CMOS bandgap with improved accuracy                             |

|      | 7.4.5   | Bruno's Bandgap                                                 |

|      | 7.4.6   | Weak Inversion Bandgap                                          |

|      | 7.4.7   | Open loop weak inversion bandgap                                |

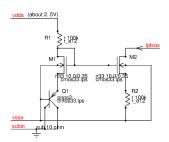

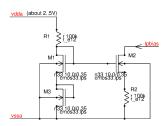

| 7.5  | Curren  | t generators                                                    |

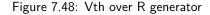

|      | 7.5.1   | VBE over R generator                                            |

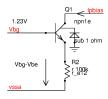

|      | 7.5.2   | Vth over R generator                                            |

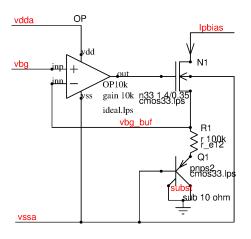

|      | 7.5.3   | Vt over R current generator                                     |

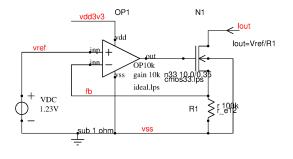

|      | 7.5.4   | Vref over R current generator                                   |

|      | 7.5.5   | NPN only ring current generator                                 |

|      | 7.5.6   | MOS ring current generator                                      |

|      | 7.5.7   | Weak inversion current generator                                |

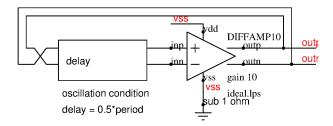

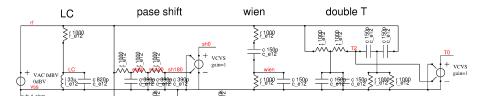

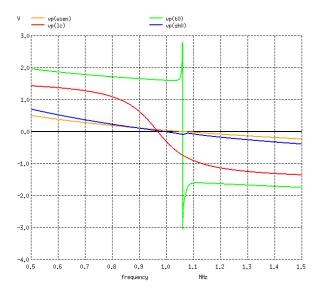

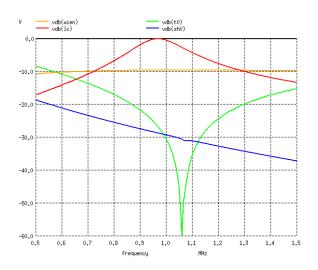

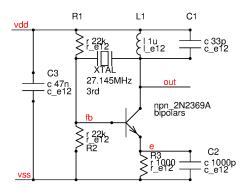

| 7.6  | Oscilla | tors                                                            |

|      | 7.6.1   | Phase shift oscillators                                         |

|      | 7.6.2   | LC oscillators                                                  |

|      | 7.6.3   | Wien oscillator                                                 |

|      | 7.6.4   | Crystal oscillators                                             |

|      | 7.6.5   | Relaxation oscillators                                          |

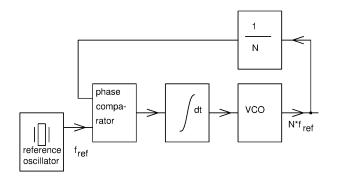

|      | 7.6.6   | PLL                                                             |

|      | 7.6.7   | Comparison of start up behavior of different oscillator types   |

|      | 7.6.8   | Clock distribution                                              |

| 7.7  |         | iers                                                            |

|      | 7.7.1   | The output stage first                                          |

|      | 7.7.2   | Trans impedance amplifier (TIA)                                 |

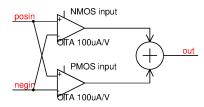

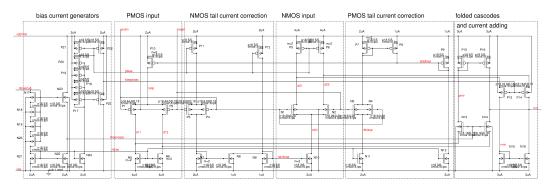

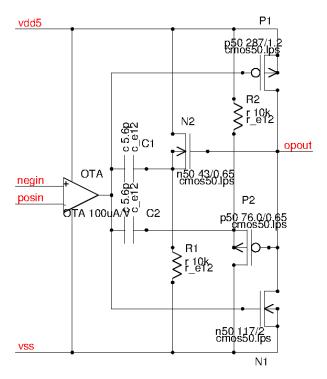

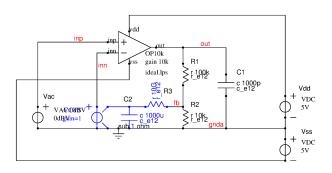

|      | 7.7.3   | Operational transconductance amplifier (OTA)                    |

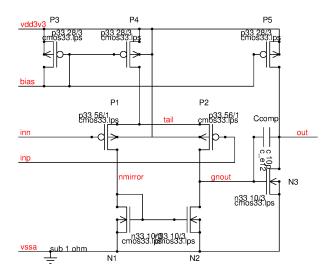

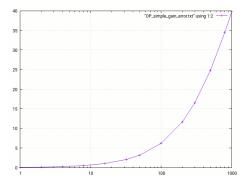

|      | 7.7.4   | Operational amplifiers (OPAMP)                                  |

|      | 7.7.5   |                                                                 |

|      | 7.7.6   | The bread & butter OPAMPs                                       |

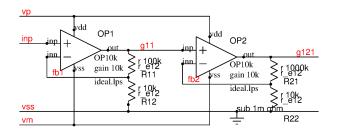

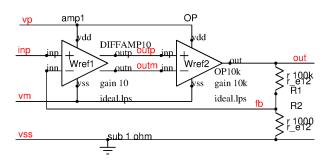

|      | 7.7.7   | Instrumentation amplifiers                                      |

|      | 7.7.8   | Fully differential amplifiers                                   |

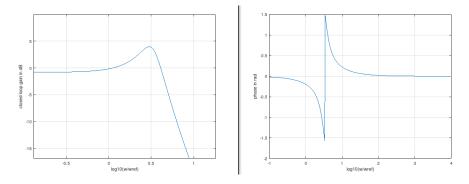

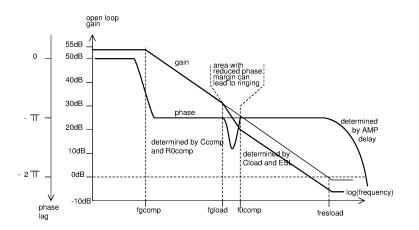

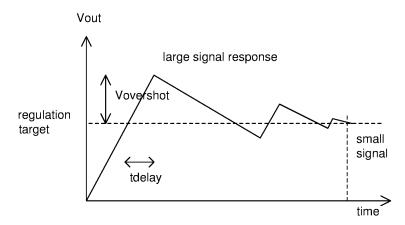

|      | 7.7.9   | Stability of an amplifier inside a regulation loop              |

|      |         | Comparators and Schmitt trigger circuits                        |

|      |         | Clocked comparators                                             |

|      |         |                                                                 |

| 70   |         | Interfacing comparators with the logic                          |

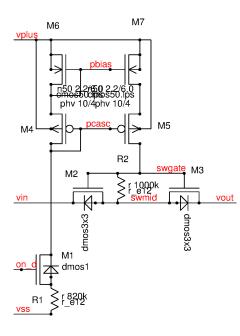

| 7.8  |         | de power output stage                                           |

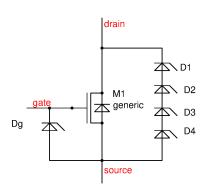

|      | 7.8.1   | Over voltage protection                                         |

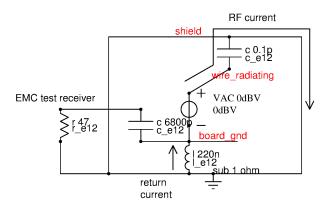

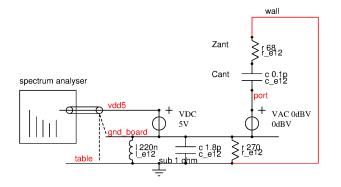

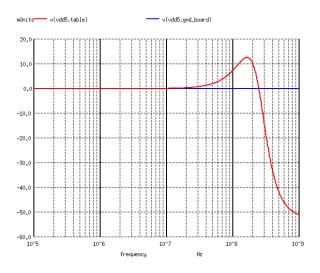

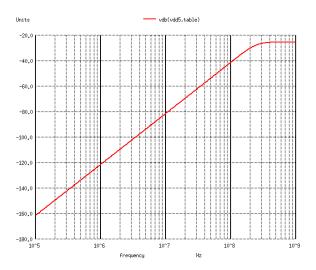

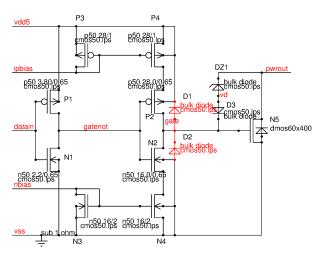

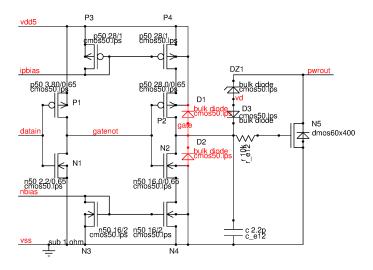

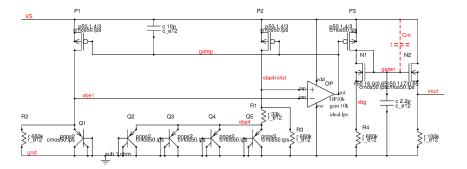

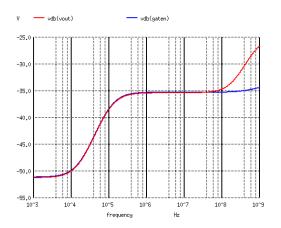

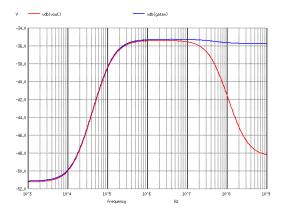

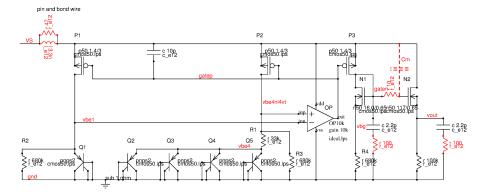

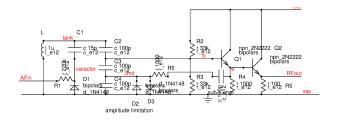

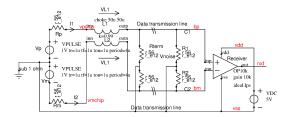

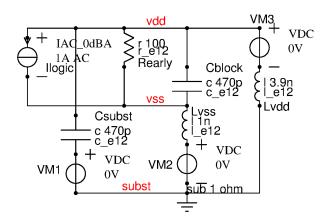

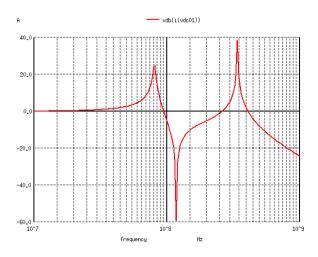

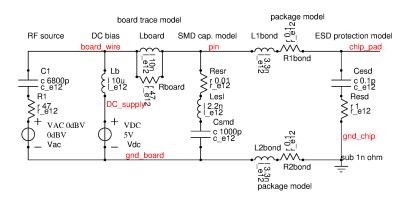

|      | 7.8.2   | RF sensitivity of a low side driver with overvoltage protection |

|      | 7.8.3   | over current protection                                         |

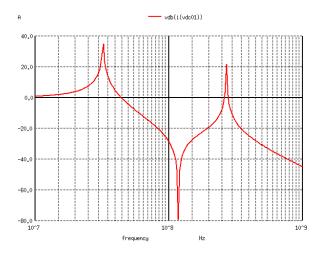

| 7.0  | 7.8.4   | RF sensitivity of the current limit circuit                     |

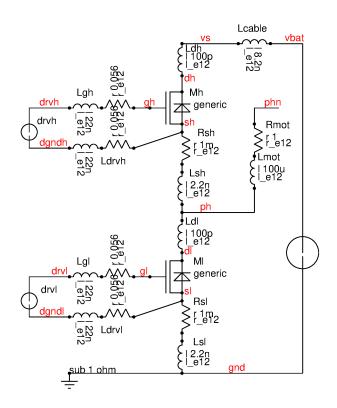

| 7.9  | -       | de power output stages                                          |

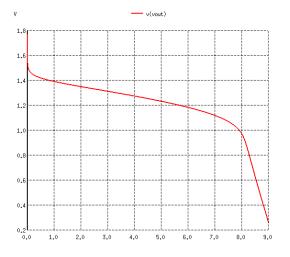

|      | 7.9.1   | High side driver operating with partial capacitive load         |

|      | 7.9.2   | High side driver operating with an inductive load               |

|      | 7.9.3   | RF injection into the NMOS HIGH side driver:                    |

|      | 7.9.4   | Bipolar solutions                                               |

|      | 7.9.5   | Floating switch driver stages                                   |

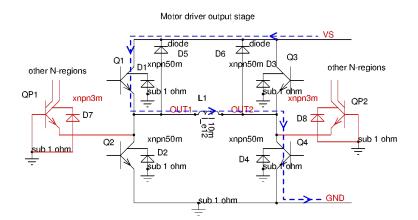

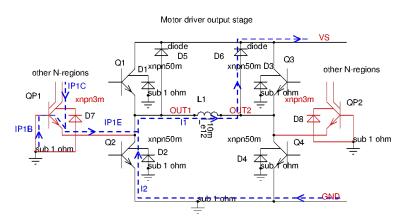

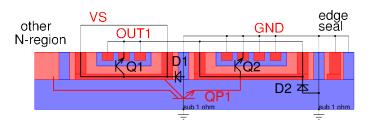

| 7.10 |         | bridges                                                         |

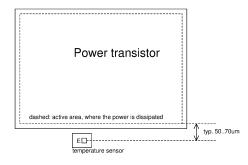

|      |         | Power transistor spread considerations                          |

|      |         | Protection of the driver stage                                  |

| 1.11 | •       | rature sensors                                                  |

|      |         | delta Vbe temperature sensor                                    |

|      |         | Vbe temperature sensor                                          |

|      |         | Using the bandgap as a temperature sensor                       |

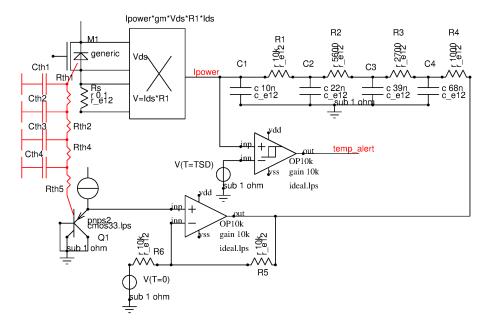

|      |         | Modeling the thermal path                                       |

| 7.12 |         | ltage protection                                                |

|      |         | Shared protection                                               |

|      |         | Tolerances of overvoltage protections                           |

| 7.13 |         | rrent protection                                                |

|      | 7.13.1  | Current measurement using a sense resistor                      |

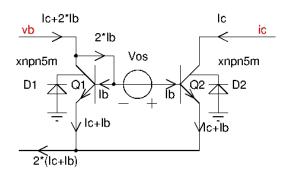

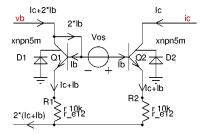

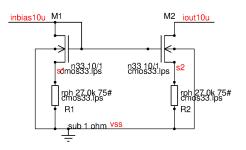

|   |      |         | Current measurement using a sense transistor:                  |

|---|------|---------|----------------------------------------------------------------|

|   |      | 7.13.3  | Desat current sense:                                           |

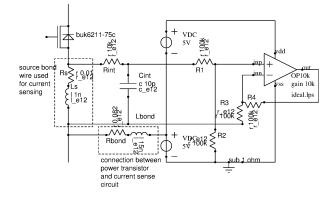

|   |      | 7.13.4  | Current measurement using the bond wires                       |

|   | 7.14 | Save o  | peration area protection (SOA protection)                      |

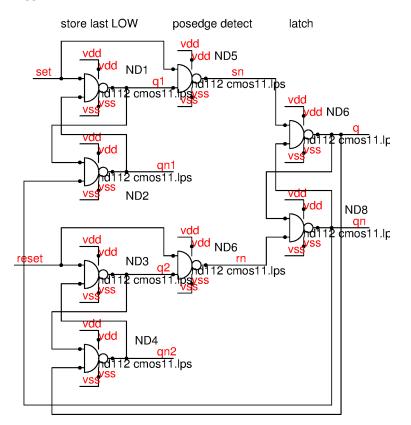

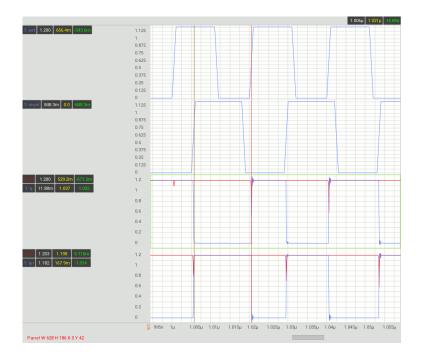

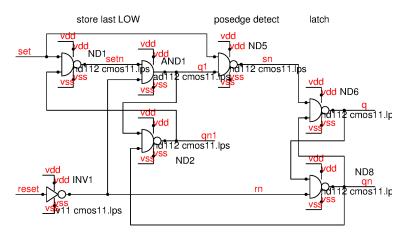

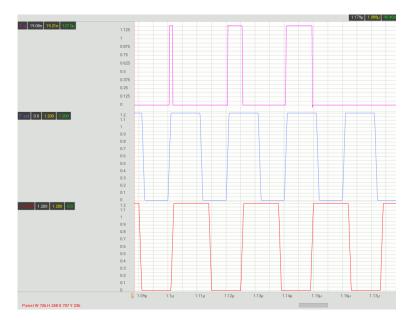

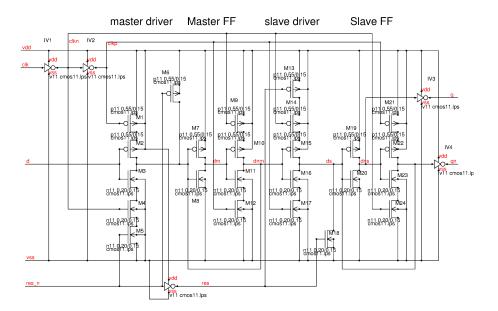

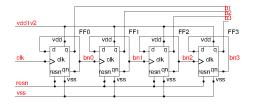

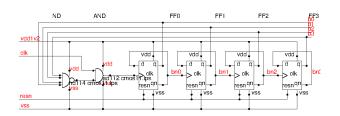

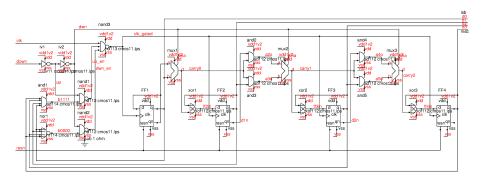

|   | 7.15 | Logic g | gates and flip flops                                           |

|   |      | 7.15.1  | Logic Synthesis                                                |

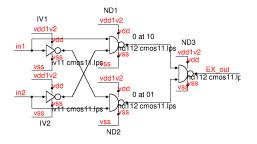

|   |      |         | Inverters                                                      |

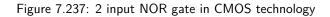

|   |      |         | NAND gates                                                     |

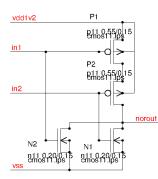

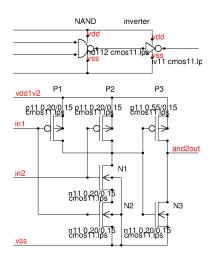

|   |      |         | NOR gates                                                      |

|   |      |         | AND gates                                                      |

|   |      |         | OR gates                                                       |

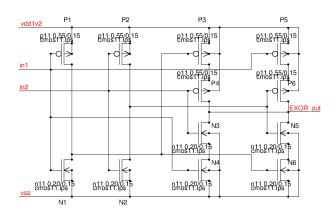

|   |      |         | EXOR gates                                                     |

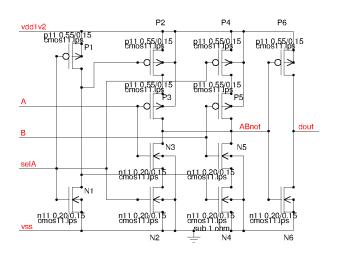

|   |      |         | Multiplexers                                                   |

|   |      |         | Latches                                                        |

|   |      |         |                                                                |

|   |      |         | ) data flip flop (DFF)                                         |

|   |      |         | I flip flops for very high speed dividers                      |

|   |      |         | 2 Counters                                                     |

|   |      |         | 3Shift registers                                               |

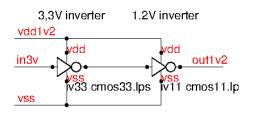

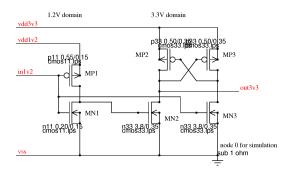

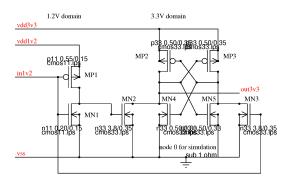

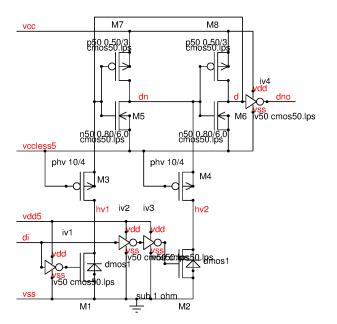

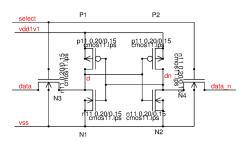

|   |      | 7.15.14 | Level shift circuits                                           |

| • | ۰.   |         | 220                                                            |

| 8 |      |         | Iding blocks 338                                               |

|   | 8.1  |         | ier applications                                               |

|   |      | 8.1.1   | Amplifier requirements                                         |

|   |      | 8.1.2   | Open loop operation                                            |

|   |      | 8.1.3   | Closed loop operation                                          |

|   |      | 8.1.4   | Noise and offset propagation in closed loop operation          |

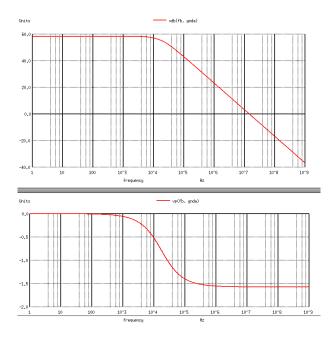

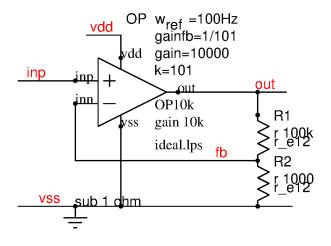

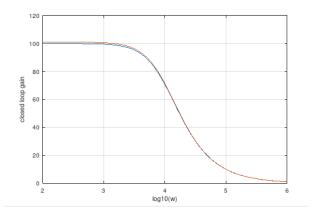

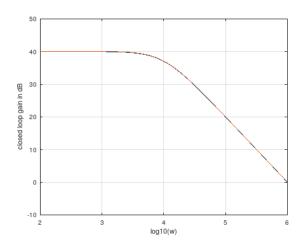

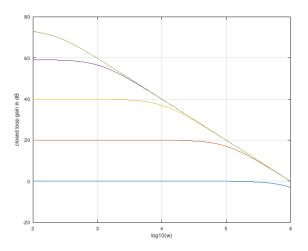

|   |      | 8.1.5   | AC characteristics of an amplifier with one pole with feedback |

|   |      | 8.1.6   | Amplifiers with two poles                                      |

|   |      | 8.1.7   | Amplifiers with low output impedance                           |

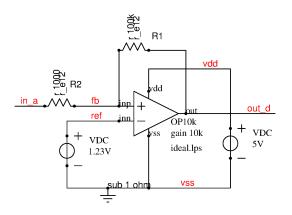

|   |      | 8.1.8   | Regulation loops                                               |

|   |      | 8.1.9   | Differentiating (D)                                            |

|   |      | 8.1.10  | PID regulator                                                  |

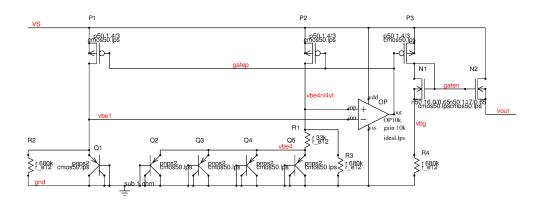

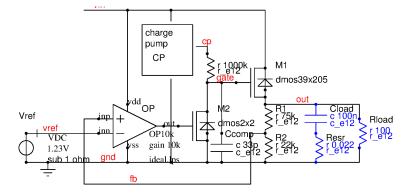

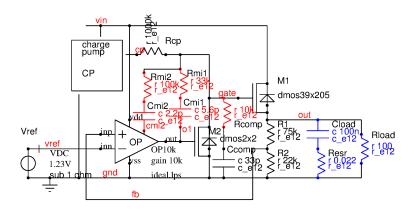

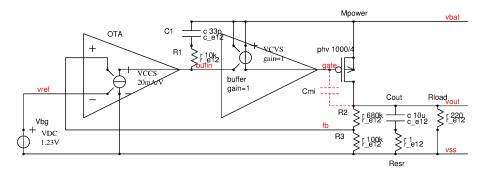

|   | 8.2  |         | e regulators                                                   |

|   |      | 8.2.1   | Unregulated prestabilizer                                      |

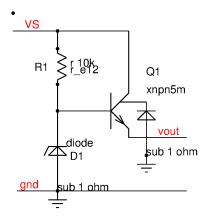

|   |      | 8.2.2   | Emitter follower voltage regulator                             |

|   |      | 8.2.3   | Source follower voltage regulator                              |

|   |      | 8.2.4   | Source follower regulator with stacked output transistors      |

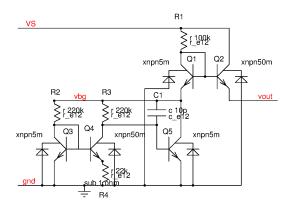

|   |      | 8.2.5   | Low drop regulators with PNP power transistors                 |

|   |      | 8.2.6   | Low drop regulators with PMOS power transistors                |

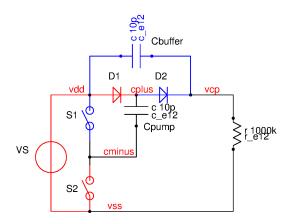

|   | 8.3  |         | pump                                                           |

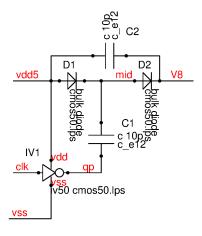

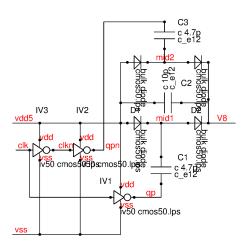

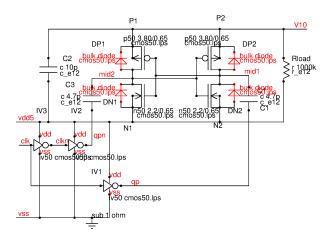

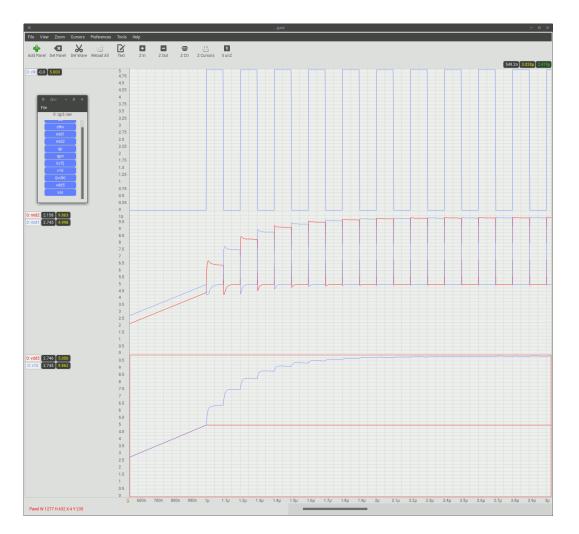

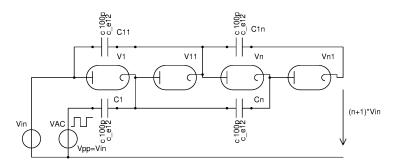

|   | 0.5  | 8.3.1   | Simplified chargepump with ideal rectifier and ideal switches  |

|   |      |         |                                                                |

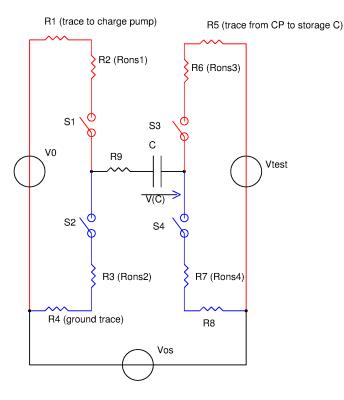

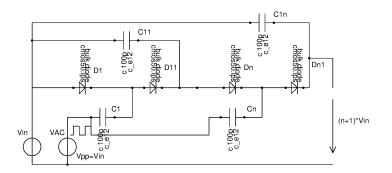

|   |      | 8.3.2   | Charge pump with resistive switches and rectifiers             |

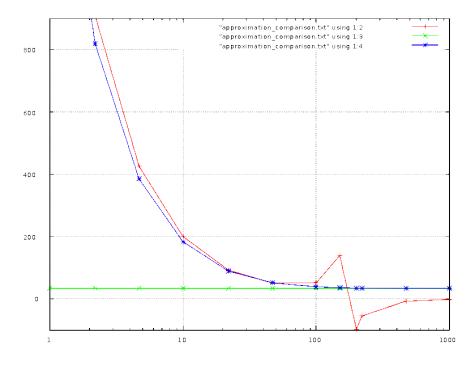

|   |      | 8.3.3   | Single frequency aproximation                                  |

|   |      | 8.3.4   | Comparison of the 3 approximations shown                       |

|   | ~ .  | 8.3.5   | Practical designs of charge pumps                              |

|   | 8.4  |         | mode power supplies                                            |

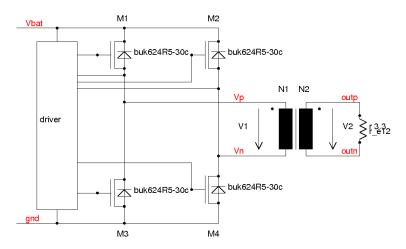

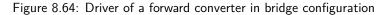

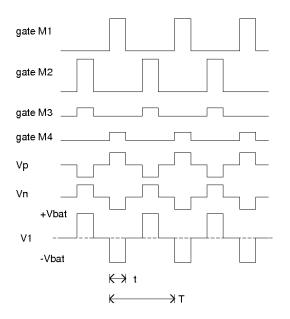

|   |      | 8.4.1   | Forward converter                                              |

|   |      | 8.4.2   | Drivers for Fluorescent lamps                                  |

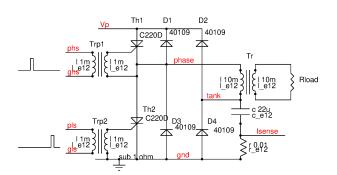

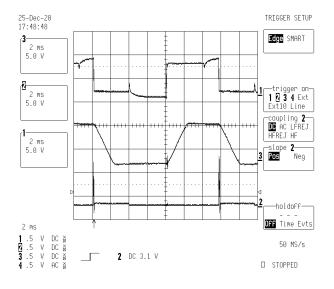

|   |      | 8.4.3   | Zero Voltage Switching (ZVS)                                   |

|   |      | 8.4.4   | Zero current switching (ZCS)                                   |

|   |      | 8.4.5   | Flyback converters                                             |

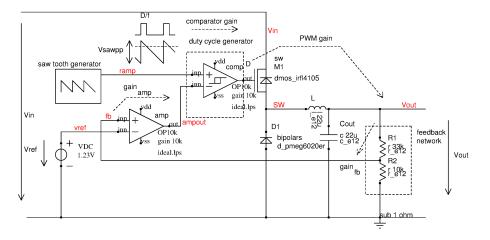

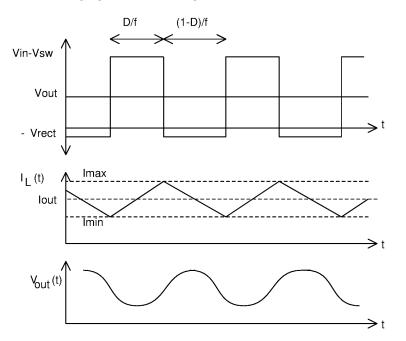

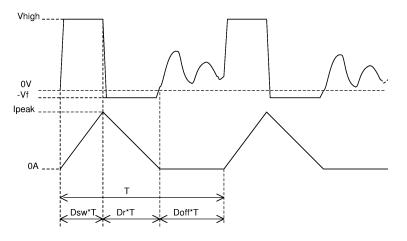

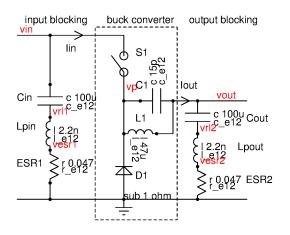

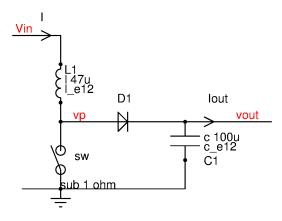

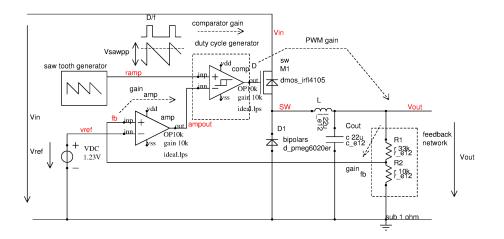

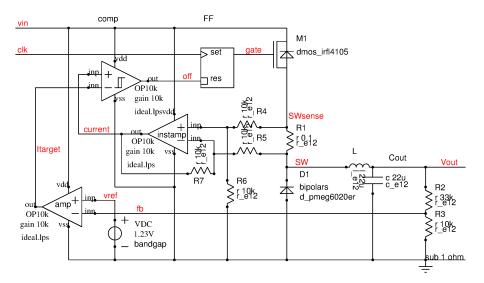

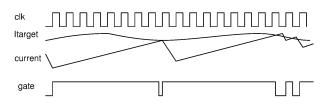

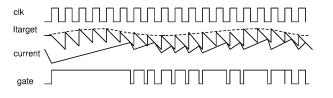

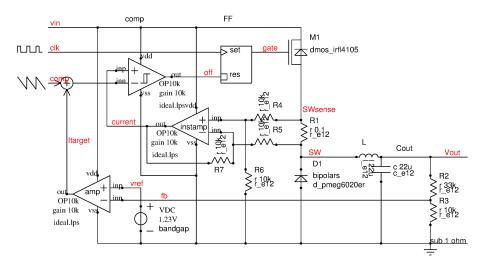

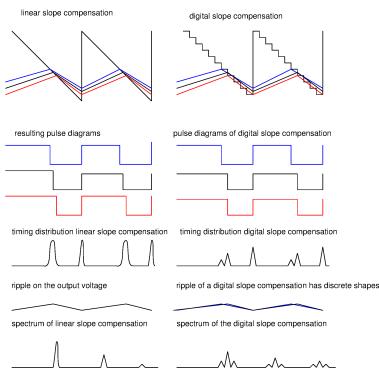

|   |      | 8.4.6   | Buck Converter (Step down)                                     |

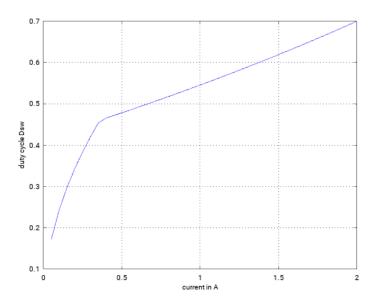

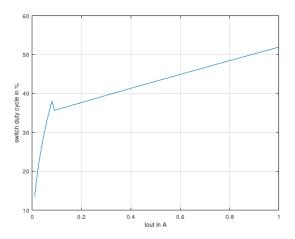

|   |      | 8.4.7   | Practical design considerations of a buck converter            |

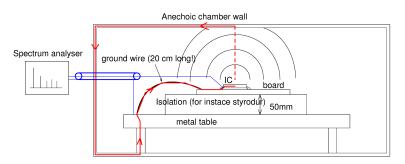

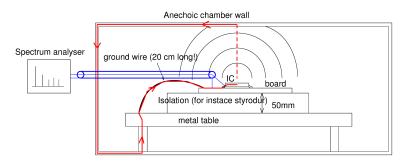

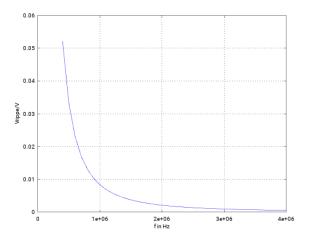

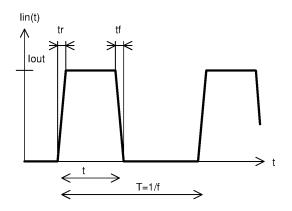

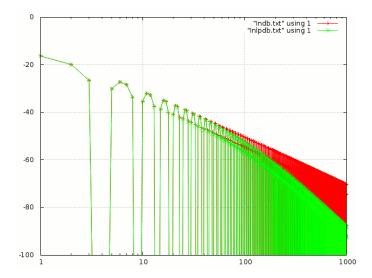

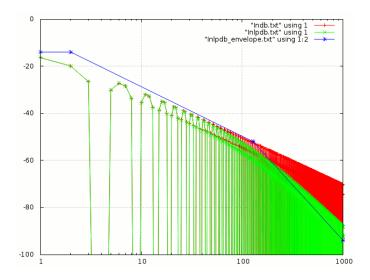

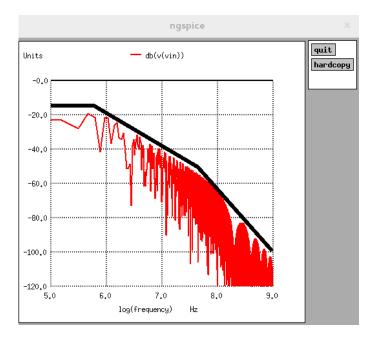

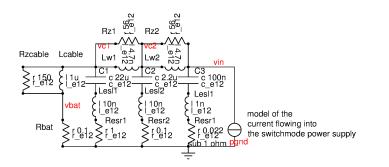

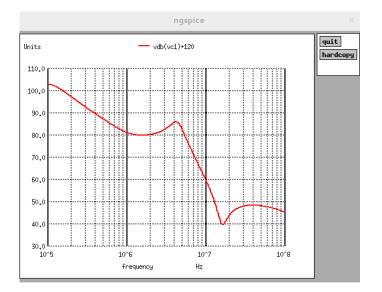

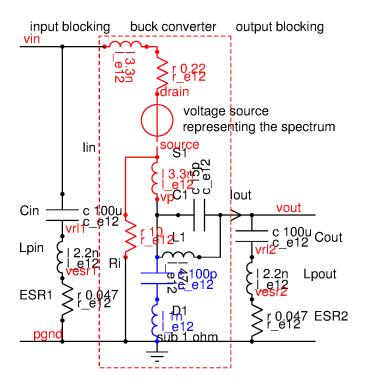

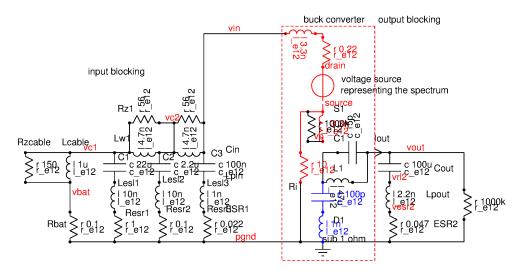

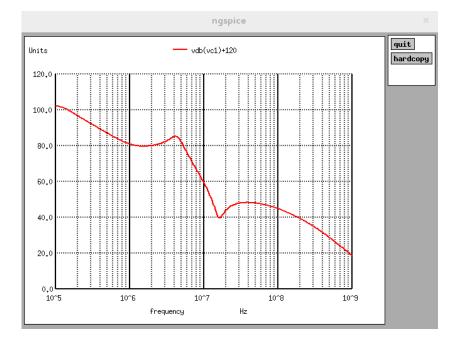

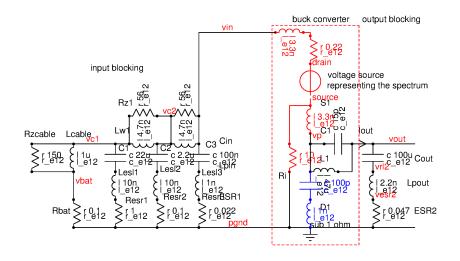

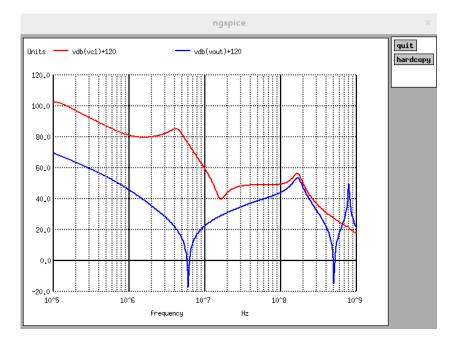

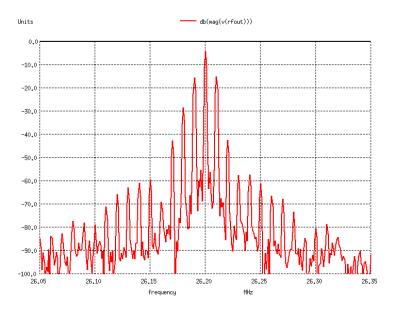

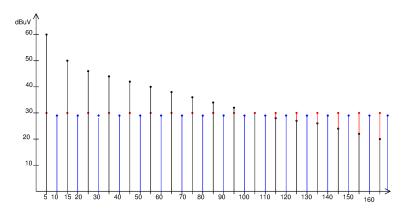

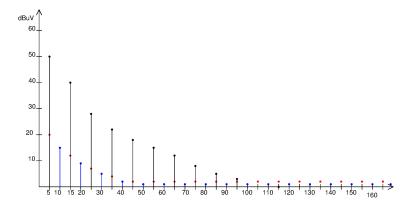

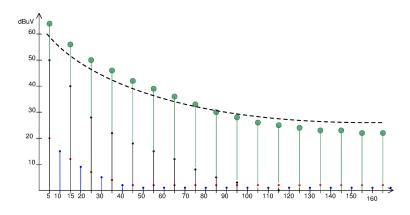

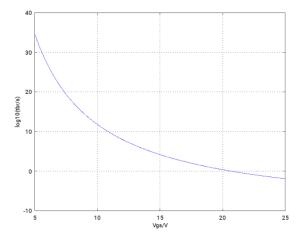

|   |      | 8.4.8   | RF emission of a buck power supply                             |

|   |      | 8.4.9   | Boost Converter                                                |

|   |      | 8.4.10  | Regulation loops                                               |

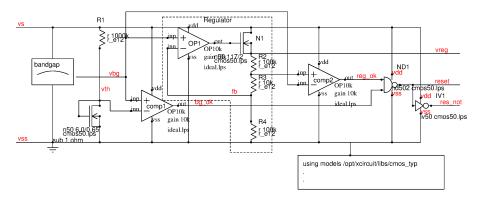

|   | 8.5  |         | and voltage monitoring circuits                                |

|   |      | 8.5.1   | Reference of a reset generator                                 |

|   |      | 8.5.2   | Functional safety                                              |

|   |      | 8.5.3   | Comparator bias                                                |

|   |      | 8.5.4   | Autonomous undervoltage detection circuits                     |

|   |      | 8.5.5   | Minimum reset time         420                                 |

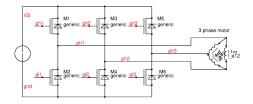

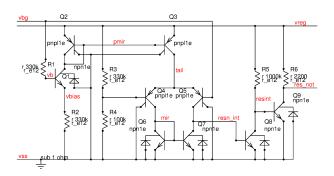

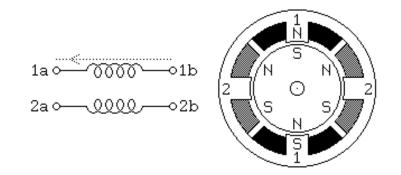

|   | 8.6  |         | r Motor Drivers                                                |

|   | 0.0  | Srehhe  |                                                                |

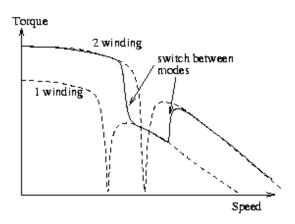

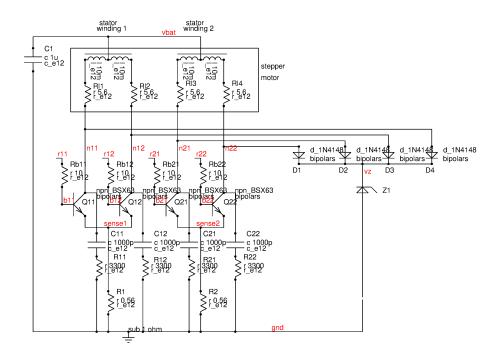

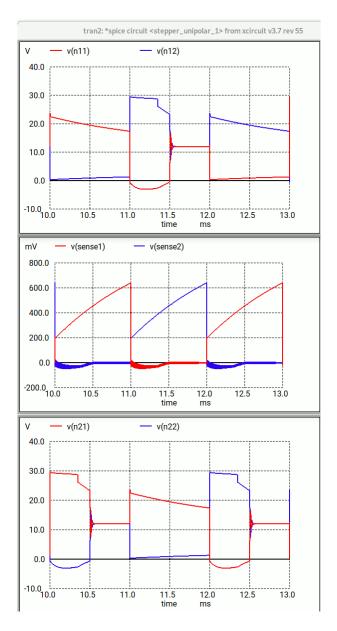

|       | 8.6.1 Unipolar drivers                                      | 34 |

|-------|-------------------------------------------------------------|----|

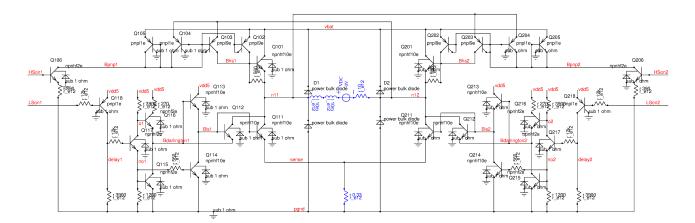

|       | 8.6.2 Bipolar Stepper Motor Driver                          |    |

|       | 8.6.3 MOS power transistor bridges                          |    |

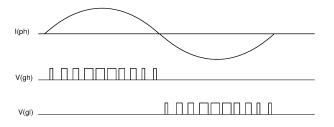

|       | 8.6.4 Cross conduction and break before make                |    |

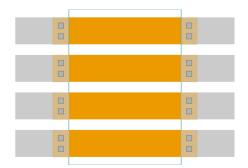

|       | 8.6.5 floorplan of stepper motor driver power stages        |    |

|       | 8.6.6 Regulation of the current                             |    |

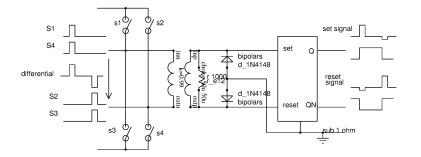

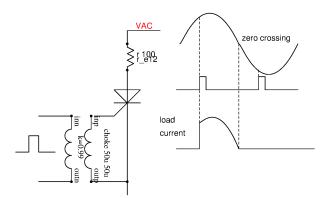

| 8.7   | Galvanic isolation circuits                                 |    |

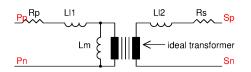

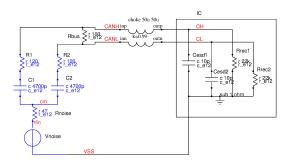

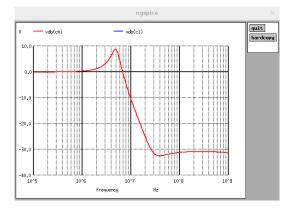

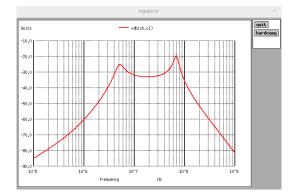

|       | 8.7.1 Transformer coupled systems                           |    |

| 8.8   | Near field communication                                    |    |

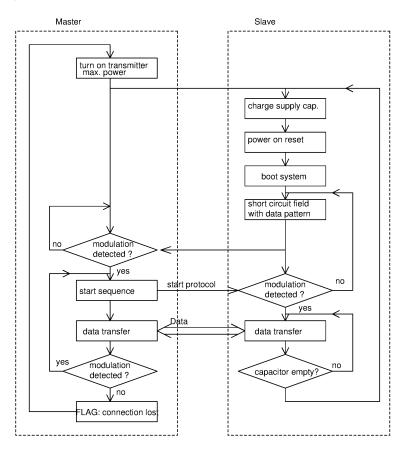

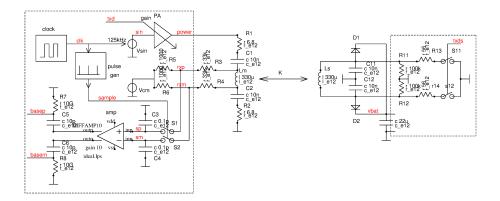

|       | 8.8.1 Passive near field communication                      |    |

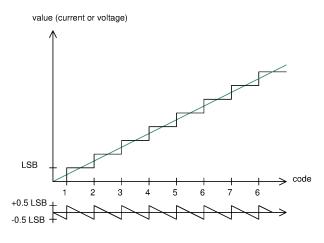

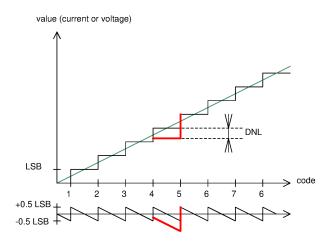

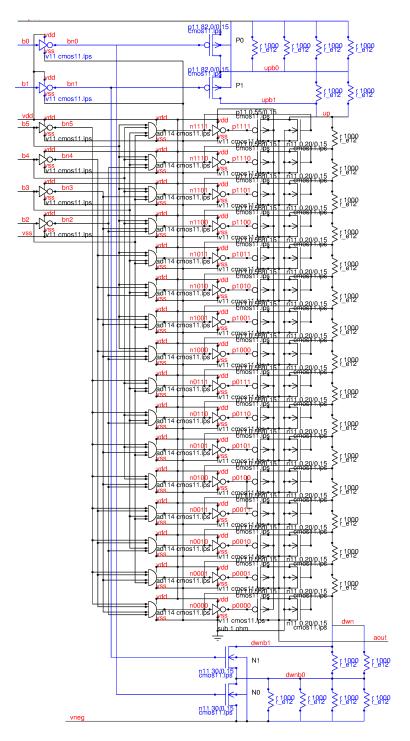

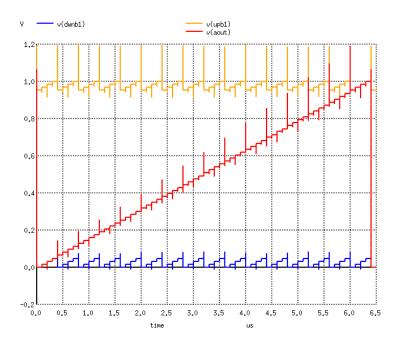

| 8.9   | Digital analog converter (DAC)                              |    |

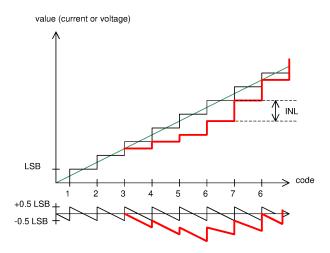

|       | 8.9.1 Error types of DACs and ADCs                          |    |

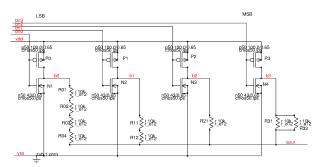

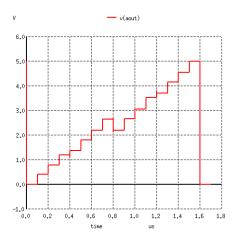

|       | 8.9.2 DAC using resistors                                   |    |

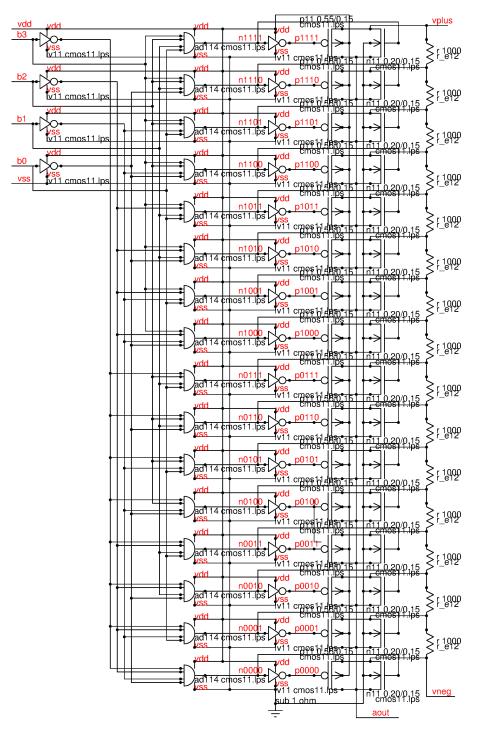

|       | 8.9.3 Current DACs                                          |    |

|       | 8.9.4 Voltage gradients in the ground wire                  |    |

|       | 8.9.5 Gain error of a DAC                                   |    |

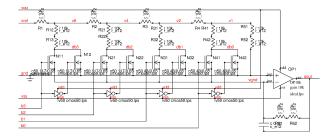

| 8.10  | ) Analog digital converter (ADC)                            |    |

|       | 8.10.1 Noise in ADCs                                        |    |

|       | 8.10.2 The most basic: a 1 bit ADC                          |    |

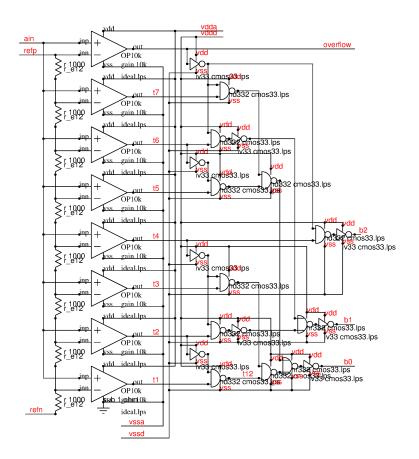

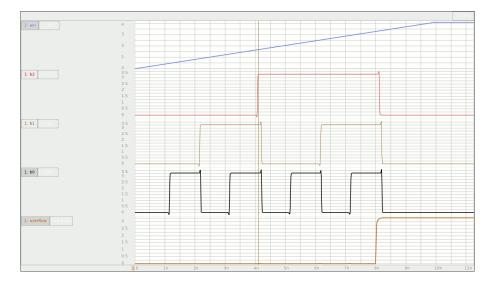

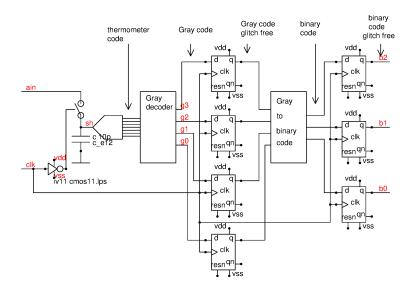

|       | 8.10.3 FLASH ADC                                            |    |

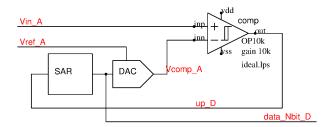

|       | 8.10.4 Successive Approximation Register (SAR) converters   |    |

|       | 8.10.5 ADCs as a load                                       | 77 |

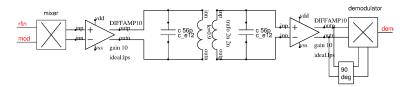

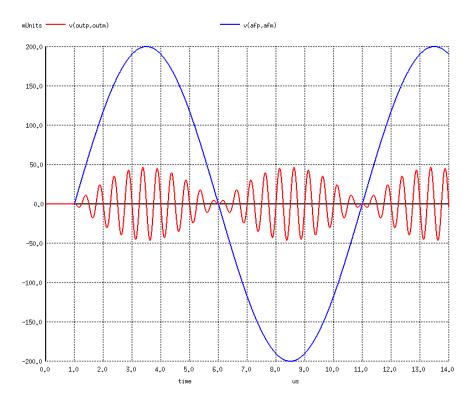

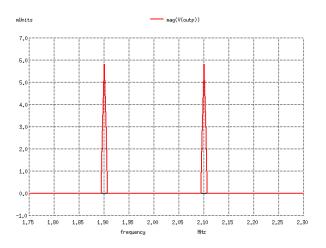

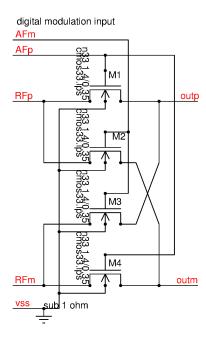

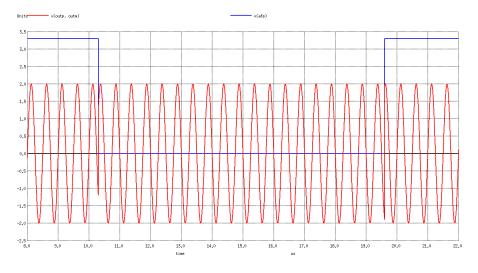

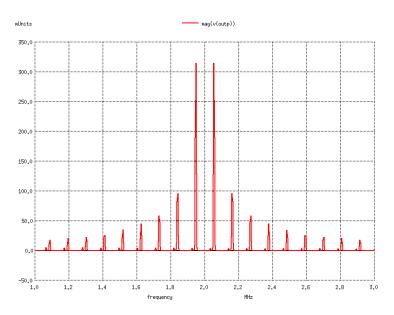

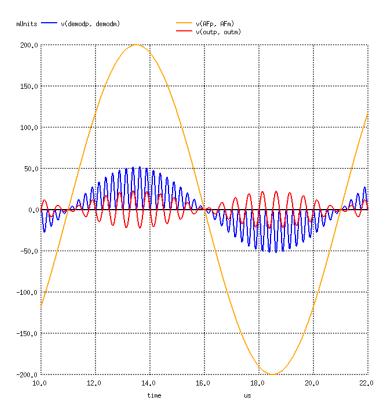

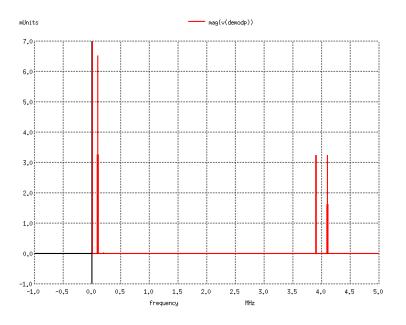

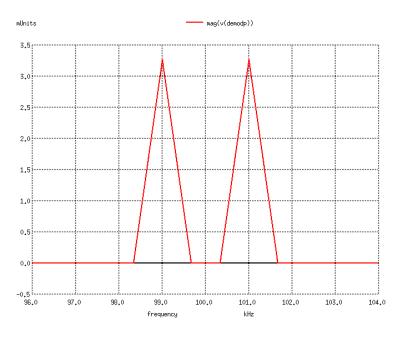

|       | 8.10.6 Amplitude modulation                                 | 78 |

|       | 8.10.7 AM demodulation                                      | 79 |

|       | 8.10.8 AM modulation with suppressed carrier                | 79 |

|       | 8.10.9 Demodulation of a DSB signal with suppressed carrier | 82 |

|       | 8.10.10 Frequency modulation (FM)                           | 84 |

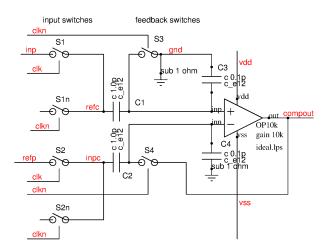

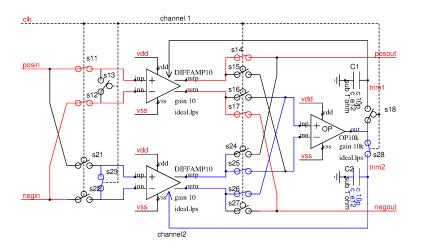

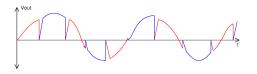

| 8.11  | Chopper stabilized amplifier                                | 85 |

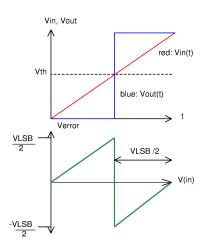

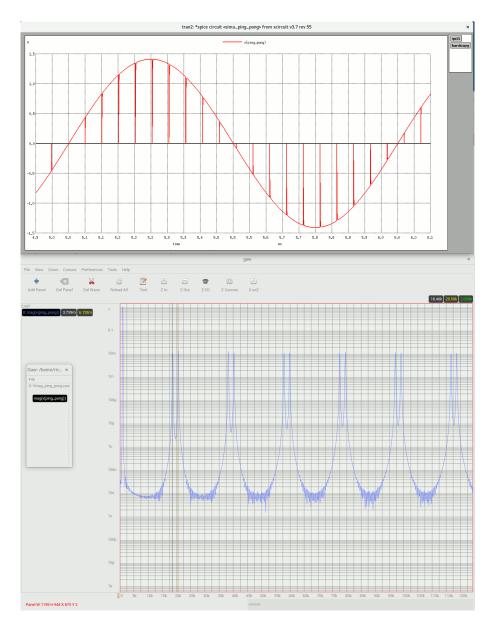

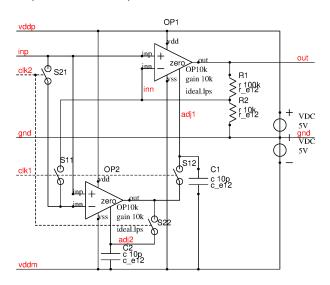

| 8.12  | 2 Auto Zero Amplifier                                       | 87 |

|       | 8.12.1 Zeroing while not in use                             | 88 |

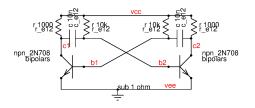

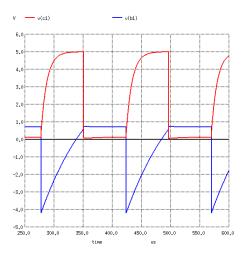

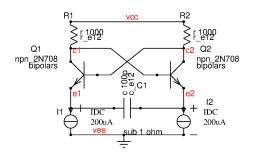

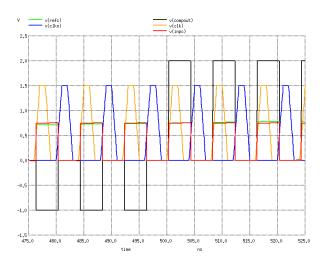

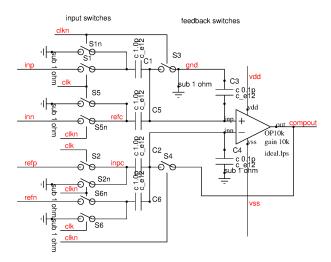

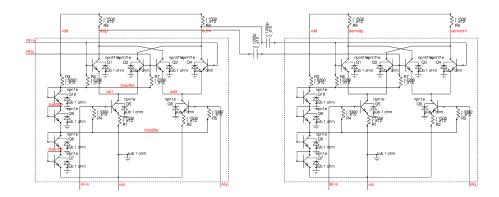

|       | 8.12.2 Ping-pong auto zero amplifier                        | 89 |

|       | 8.12.3 In the loop auto zero                                | 92 |

|       | 8.12.4 Beyond all measures                                  | 93 |

| 8.13  | B Input and output cells (IO cell)                          | 94 |

|       | 8.13.1 Standard logic IO cells                              | 94 |

|       | 8.13.2 Digital IO cells for extended voltage ranges         | 95 |

|       | 8.13.3 LIN                                                  | 99 |

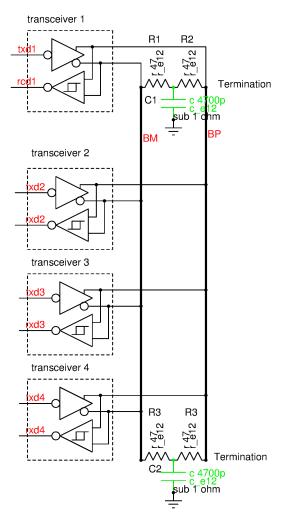

|       | 8.13.4 Differential signal interfaces overview              | 00 |

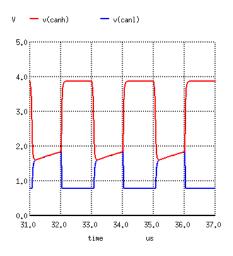

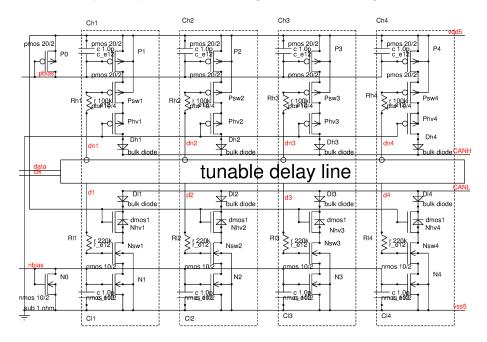

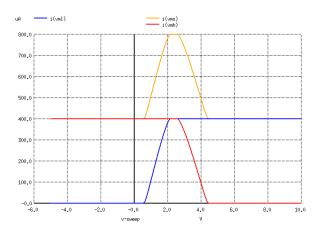

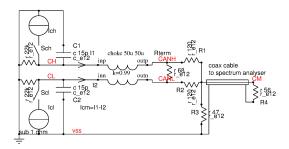

|       | 8.13.5 CAN                                                  |    |

|       | 8.13.6 Flexray                                              | 09 |

|       | 8.13.7 USB                                                  |    |

|       | 8.13.8 Ethernet PHYs                                        |    |

|       | 8.13.9 Test IOs                                             |    |

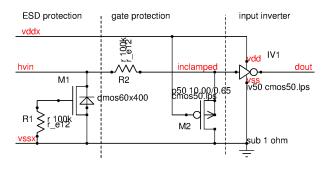

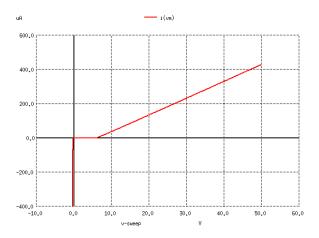

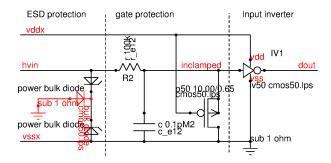

| 8.14  | ESD protection                                              |    |

|       | 8.14.1 Destruction mechanisms to protect against            |    |

|       | 8.14.2 ESD models                                           |    |

|       | 8.14.3 ESD protection circuits                              |    |

|       |                                                             |    |

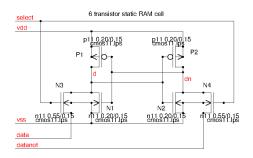

| 9 Rar | Idom access memories and registers 52                       | 20 |

|       | 9.0.1 Data line capacity                                    | 22 |

|       | 9.0.2 Refreshing                                            | 23 |

| 9.1   | Static RAM cell                                             | 24 |

| 9.2   | Registers                                                   | 25 |

|       |                                                             |    |

|       |                                                             | 25 |

|       | Zener zap                                                   |    |

| 10.2  | 2 Laser trimming                                            |    |

|       | 10.2.1 Poly silicon fuse                                    |    |

|       | 10.2.2 Thin film resistor trimming                          |    |

| 10.3  | B Memresistor                                               |    |

| 10.4  | EEPROM                                                      |    |

|       | 10.4.1 SLC single level cell                                |    |

|       | 10.4.2 MLC multi level cell                                 | 25 |

|    |             | 10.4.3 TLC tripple level cell                            |            |

|----|-------------|----------------------------------------------------------|------------|

|    |             | 10.4.4 Pseudo-SLC (pSLC)                                 |            |

|    | 10.5        | Cross point memory                                       | 26         |

|    |             |                                                          |            |

| 11 | Back        | c on the Top Level 52                                    | 26         |

|    | 11.1        | The package                                              | 26         |

|    | 11.2        | ESD considerations                                       | 26         |

|    |             | Electromagnetic emission considerations                  |            |

|    |             | 11.3.1 EME System point of view                          |            |

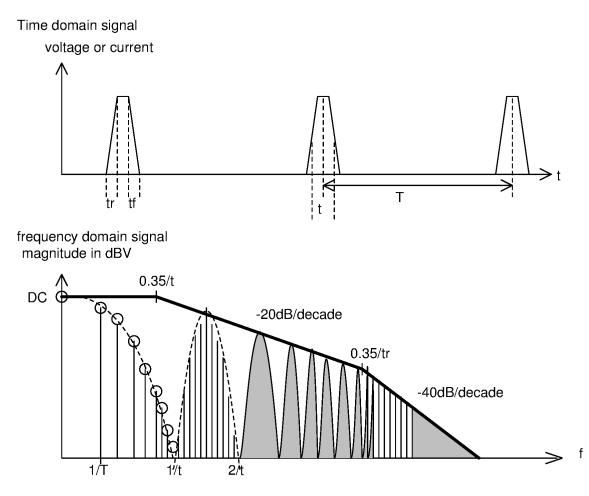

|    |             | 11.3.2 Logic acting as an RF source                      |            |

|    | 11 <i>A</i> | Electromagnetic sensitivity considerations               |            |

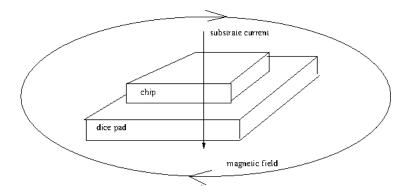

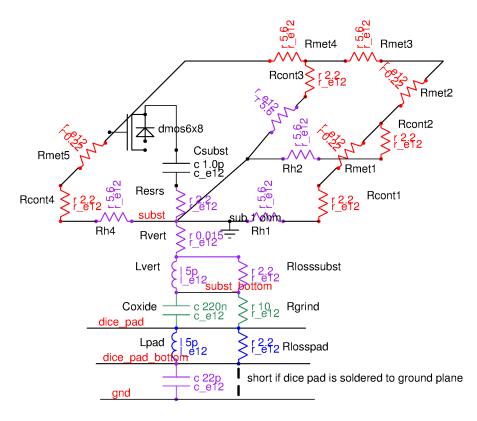

|    | 11.7        | 11.4.1 Low resistive substrate and exposed dice pad      |            |

|    |             |                                                          | ) [        |

| 12 | Test        | ing of intergrated circuits 53                           | 22         |

| 14 |             | Testing in the laboratory                                |            |

|    | 12.1        | 12.1.1 Sample preparation and modification methods       |            |

|    |             |                                                          |            |

|    |             | 12.1.2 Functional tests                                  |            |

|    | 10.0        | 12.1.3 Reliability and life time tests                   |            |

|    |             | Connectivity test                                        |            |

|    | 12.3        | Scan test                                                |            |

|    |             | 12.3.1 Test coverage                                     |            |

|    |             | 12.3.2 Testing at speed                                  |            |

|    | 12.4        | Joint Test Action Group (JTAG)                           | 37         |

|    |             | 12.4.1 JTAG modes                                        | 37         |

|    |             | 12.4.2 JTAG testers                                      | 38         |

|    |             | 12.4.3 JTAG connectors                                   | 39         |

|    | 12.5        | Built in self test (BIST)                                |            |

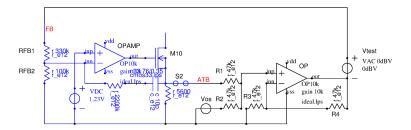

|    |             | Analog test bus (ATB)                                    |            |

|    |             | 12.6.1 Design considerations                             |            |

|    |             | 12.6.2 A practical example                               |            |

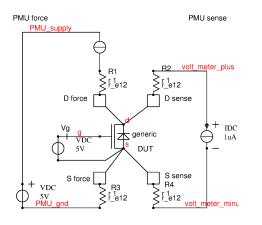

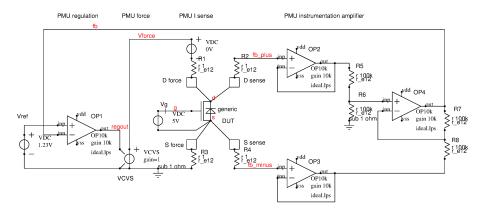

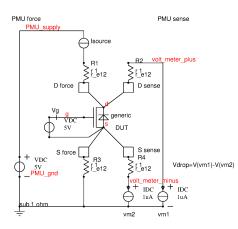

|    | 127         | Power transistor test modes                              |            |

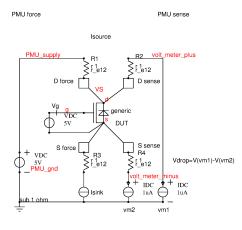

|    | 12.1        | 12.7.1 Sense and force                                   |            |

|    |             | 12.7.2 Quasi differential measurements                   |            |

|    |             |                                                          |            |

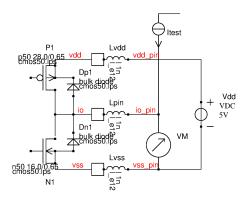

|    |             | 12.7.3 Ron test                                          |            |

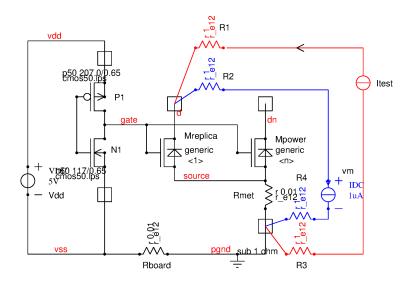

|    |             | 12.7.4 Replica transistor test                           |            |

|    |             | 12.7.5 gate stress test                                  |            |

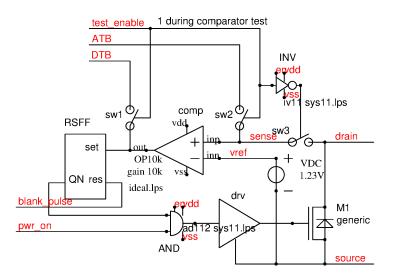

|    |             | 12.7.6 current limit test                                |            |

|    |             | 12.7.7 void test                                         |            |

|    |             | 12.7.8 bond wire test                                    |            |

|    | 12.8        | Amplifier testing                                        | 52         |

|    | 12.9        | Security rules                                           | 55         |

|    |             | 12.9.1 Encrypted access to test modes                    | 56         |

|    |             | 12.9.2 Protection using write protect bits               | 56         |

|    |             | 12.9.3 Read protection and write protection              |            |

|    |             | 12.9.4 Read and write protection + parity                |            |

|    |             | 12.9.5 Central kill                                      |            |

|    |             | 12.9.6 Summary of test mode access protections           |            |

|    | 12 10       | Dinterpretation of test results                          |            |

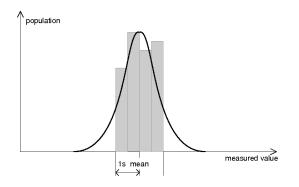

|    | 12.10       | 12.10.1 Calculating with Gaussian distributions          |            |

|    | 10.1        | •                                                        |            |

|    |             | LSearching defects and break downs with optical emission |            |

|    | 12.12       | 2Test equipment maintenance                              |            |

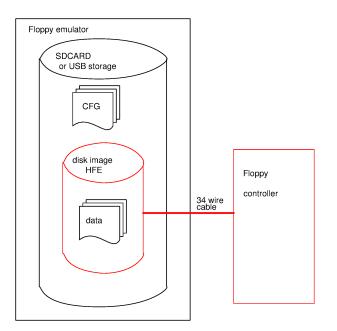

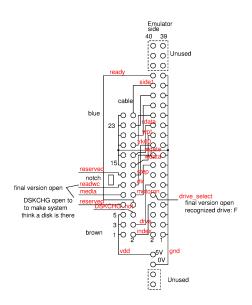

|    |             | 12.12.1 Floppy disk replacement                          |            |

|    |             | 12.12.2 Equipment control using LAN                      | )2         |

| 10 | -           |                                                          |            |

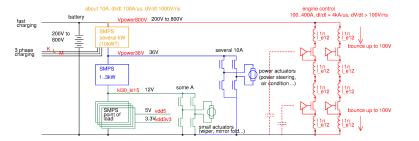

| 13 |             | gy supply 56                                             |            |

|    | 13.1        | Where does the energy come from                          |            |

|    |             | 13.1.1 Some efficiency standards to consider             |            |

|    |             | 13.1.2 Future trends of energy storage                   |            |

|    |             | 13.1.3 Future concepts of supplying mobile applications  | j5         |

|    |             | 13.1.4 Super capacitors                                  | <u>5</u> 8 |

|    | 13.2        | Pollution                                                | 58         |

|    |             | 13.2.1 Burning coal                                      | 58         |

|    |             | 13.2.2 Burning Natural gas                               |            |

|    |             |                                                          |            |

|    |       | 13.2.3   | Burning liquid fuels                                                                                                                                         |     |     | •••   |     |     |     |   |     | 570   |

|----|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----|-----|-----|---|-----|-------|

|    |       | 13.2.4   | Using electric energy                                                                                                                                        |     |     |       |     |     |     |   |     | 571   |

|    |       | 13.2.5   | Cost of pullution                                                                                                                                            |     |     |       |     |     |     |   |     | 572   |

|    |       | 13.2.6   | Conclusion of the comparison                                                                                                                                 |     |     |       |     |     |     |   |     | 572   |

|    | 13.3  | Energy   | distribution                                                                                                                                                 |     |     |       |     |     |     |   |     | 572   |

|    |       |          | Branche currents and wire currents                                                                                                                           |     |     |       |     |     |     |   |     |       |

|    | 13.4  |          | ement of an energy distribution system                                                                                                                       |     |     |       |     |     |     |   |     |       |

|    |       | 0        | pances                                                                                                                                                       |     |     |       |     |     |     |   |     |       |

|    | 10.0  |          | Solar magnetic storms                                                                                                                                        |     |     |       |     |     |     |   |     |       |

|    |       |          | Nuclear Electromagnetic pulse                                                                                                                                |     |     |       |     |     |     |   |     |       |

|    |       |          | Direct lightning strike                                                                                                                                      |     |     |       |     |     |     |   |     |       |

|    |       |          |                                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       |          | Indirect lightning strike                                                                                                                                    |     |     |       |     |     |     |   |     |       |

|    |       |          | Spark discharges during operation and RF injection during operation                                                                                          |     |     |       |     |     |     |   |     |       |

|    |       |          | Plasma induced interference                                                                                                                                  |     |     |       |     |     |     |   |     |       |

|    |       |          | Fields of an inductive charging device                                                                                                                       |     |     |       |     |     |     |   |     |       |

|    | 13.6  | CISPR    | $RF \text{ emission limits } \ldots $ | • • | • • | • •   |     |     |     | • | • • | 578   |

|    |       |          |                                                                                                                                                              |     |     |       |     |     |     |   |     | F 7 0 |

| 14 |       |          | operties of material used in semi conductor processe                                                                                                         |     |     |       |     |     |     |   |     | 578   |

|    |       |          | mportant physical constants                                                                                                                                  |     |     |       |     |     |     |   |     |       |

|    | 14.2  |          |                                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       |          | Density (specific weight)                                                                                                                                    |     |     |       |     |     |     |   |     |       |

|    |       |          | Elasticy of materials used in semiconductor manufacturing $\ldots$ .                                                                                         |     |     |       |     |     |     |   |     |       |

|    | 14.3  |          | al parameters                                                                                                                                                |     |     |       |     |     |     |   |     |       |

|    |       | 14.3.1   | Thermal conductivity of various materials                                                                                                                    |     |     | •••   |     |     |     |   |     | 580   |

|    |       | 14.3.2   | Thermal capacity of various materials                                                                                                                        |     |     | · • · |     |     |     |   |     | 580   |

|    |       | 14.3.3   | Thermal voltages (Seebeck coefficients)                                                                                                                      |     |     |       |     |     |     |   |     | 580   |

|    | 14.4  | Electric | cal parameters                                                                                                                                               |     |     |       |     |     |     |   |     | 581   |

|    |       |          | Most important units                                                                                                                                         |     |     |       |     |     |     |   |     |       |

|    |       |          | Electrical resistivity of wiring material                                                                                                                    |     |     |       |     |     |     |   |     |       |

|    |       |          | Carrier mobilities                                                                                                                                           |     |     |       |     |     |     |   |     |       |

|    |       |          | Saturation velocity                                                                                                                                          |     |     |       |     |     |     |   |     |       |

|    |       |          | Typical resistivities found in semiconductor materials                                                                                                       |     |     |       |     |     |     |   |     |       |

|    |       |          | Dielectric constants                                                                                                                                         |     |     |       |     |     |     |   |     |       |

|    |       |          | Typical break down field strengths                                                                                                                           |     |     |       |     |     |     |   |     |       |

|    |       |          |                                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       |          | Table of Permeabilities                                                                                                                                      |     |     |       |     |     |     |   |     |       |

|    |       | 14.4.9   | Bandgap energies and bandgap voltages usually found at 300K                                                                                                  | • • | • • | • •   | ••• | • • | • • | • | • • | 582   |

| 15 | Δnn   | ondiv    | Mathematical rules                                                                                                                                           |     |     |       |     |     |     |   |     | 582   |

| 13 | •••   |          | itic equations                                                                                                                                               |     |     |       |     |     |     |   |     |       |

|    |       |          |                                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       |          |                                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       |          | polic functions                                                                                                                                              |     |     |       |     |     |     |   |     |       |

|    |       | 5        | m differentiation                                                                                                                                            |     |     |       |     |     |     |   |     |       |

|    |       |          | ution in differentiations                                                                                                                                    |     |     |       |     |     |     |   |     |       |

|    |       | -        | hmic differentiation and integration                                                                                                                         |     |     |       |     |     |     |   |     |       |

|    |       |          | itiation product rule                                                                                                                                        |     |     |       |     |     |     |   |     |       |

|    |       |          | itial quotient rule                                                                                                                                          |     |     |       |     |     |     |   |     |       |

|    | 15.9  | Logarit  | hmic differentiation                                                                                                                                         |     |     | · • · |     |     |     |   |     | 584   |

|    | 15.10 | )Basic i | ntegration rules                                                                                                                                             |     |     | •••   |     |     |     |   |     | 584   |

|    | 15.11 | 1Integra | tion using substitution                                                                                                                                      |     |     |       |     |     |     |   |     | 584   |

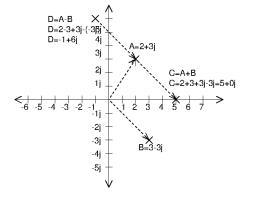

|    | 15.12 | 2Using o | complex numbers                                                                                                                                              |     |     |       |     |     |     |   |     | 585   |

|    |       |          | . Multiplication of complex numbers                                                                                                                          |     |     |       |     |     |     |   |     |       |

|    |       |          | Using complex numbers to describe reactances                                                                                                                 |     |     |       |     |     |     |   |     |       |

|    | 15 13 |          | e transformation                                                                                                                                             |     |     |       |     |     |     |   |     |       |

|    | 10.10 | •        | Stability of a transfer function:                                                                                                                            |     |     |       |     |     |     |   |     |       |

|    |       |          | Calculation of the response to an excitation in the frequency domain                                                                                         |     |     |       |     |     |     |   |     |       |

|    |       |          | BLimits of the Laplace transformation                                                                                                                        |     |     |       |     |     |     |   |     |       |

|    |       | TO.TO.   |                                                                                                                                                              | ••• | • • | • •   | • • |     | • • | • |     | 790   |

# 1 Preface

'Analog IC design – the obsolete book' – So why is it obsolete and I write it nevertheless? Probably because I am a nerd writing useless stuff for other nerds. No, not quite. The truth is analog ICs are almost extinct like relays, valves, discrete transistors..... All these things now are part of system integration.

Analog design does not scale with the advances of modern technologies. So manufacturers tend to push more and more functionality into the digital design. Today's so called analog chips consist of some 10K analog transistors together with some millions of digital gates on one chip. But those 10K analog transistors may well consume the same area as the 2 million gate logic sitting on the same dice.

So why am I writing about analog design is stead of mixed signal? Because my digital know how is ridiculously low.

How did I learn analog design? To tell you the truth: I never did! In the old days we learned about telegraphy equations, power plants, acoustics, electrical networks, how to build digital filters with the legendary PDP11..... And I had some data books holding transistor level circuits of pioneers like Bob Widlar or Bruno Murari. Later I even met some of them (So now you can guess the color of the hair I am loosing) and learned some more circuits.

In the beginning this wasn't a book. It was a collection of drawings I used to train younger engineers starting on the field of analog chip design. By the time I figured out I have to add comments to the drawings. Slowly the collection of drawings turned into an unorganized book...

Today I'm often confronted with the question: W.T.F. ! I know I have solved that some years ago, but I forgot the most important considerations and equations!

So today I'm writing this book for myself to document how I solved all the stuff that keeps repeating again and again.

This isn't really a scientific book. I don't see a point in poking out the last percent while I exactly know production spread is magnitudes higher than what I optimize. For this reason it doesn't make sense to develop equations that describe 3rd order effects. This book is more something like a cook book. If you need more details look at the literature index.

# 1.1 Using the book

The book holds some equations I regard as essential. In the recent years I found out that the mathematical education of students today seems to have fallen way behind my own mathematical education. Some of this degradation seems to be caused by the PISA comparison mechanism and not by the students themselves. (PISA tests the capability of reproducing rather than the ability of finding new solutions to compare education levels in Europe. I think this is a fatal approach because it doesn't support engineering creativity.) To give some basic mathematical help for younger engineers I added the mathematical appendix without giving any mathematical proofs (so again it is a cook book. For further details I suggest having a look at[16]).

# 1.2 If you find mistakes

The book was written without any help of editors or proof readers. I would be surprised if there are no mistakes. In case you find severe mistakes please let me know so I can correct them. The book is a living document. I will keep writing and updating. Updates will be made available time after time on my WEB page.

# 1.3 Copying

The contents of this book is publicly known from earlier publications (Some circuits in fact date back to the 1920s!). Nothing new under the sun. Since I learned that licenses owned by publishing companies have become a major obstacle for public education at schools and universities today this book intentionally is free.

- No publishing company and no other editors are involved in this book project.

- All figures were drawn by myself (in most cases using public domain software to avoid any conflicts) and are free.

- You may make copies

- You may distribute copies provided you name the source (Title, author, year of the revision)

- You may include pages of this book in your own presentations provided you name the source (Title, author, year of the revision)

- You may convey a work based on this book, provided that you also meet all of these conditions:

- a) The work must carry prominent notices stating that you modified it, and giving a relevant date.

b) The work must carry prominent notices stating that it is released free for public use including copying and conveying it.

c) You must license the entire work, as a whole, under the same conditions as this book to anyone who comes into possession of a copy.

# 1.4 Warranty and Liability

The book holds simplified (conceptual) schematics, drawings and some code snippets. These simplified examples can't be expected to be fool proof for a chip integration. In most cases you will need to enhance them (adding power down, test modes etc.) to really make them fit to your application.

• Disclaimer of Warranty:

THERE IS NO WARRANTY FOR THE PROGRAM OR SCHEMATIC, TO THE EXTENT PERMITTED BY APPLICABLE LAW. EXCEPT WHEN OTHERWISE STATED IN WRITING THE COPYRIGHT HOLDERS AND/OR OTHER PARTIES PROVIDE THE PROGRAM OR SCHEMATIC "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE PROGRAM OR SCHEMATIC IS WITH YOU. SHOULD THE PROGRAM OR SCHEMATIC PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR CORRECTION.

• Limitation of Liability.

IN NO EVENT UNLESS REQUIRED BY APPLICABLE LAW OR AGREED TO IN WRITING WILL ANY COPYRIGHT HOLDER, OR ANY OTHER PARTY WHO MODIFIES AND/OR CONVEYS THE PROGRAM OR SCHEMATIC AS PERMITTED ABOVE, BE LIABLE TO YOU FOR DAMAGES, INCLUDING ANY GENERAL, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE PROGRAM OR SCHEMATIC (INCLUDING BUT NOT LIMITED TO LOSS OF DATA OR DATA BEING RENDERED INACCURATE OR LOSSES SUSTAINED BY YOU OR THIRD PARTIES OR A FAILURE OF THE PROGRAM OR SCHEMATIC TO OPERATE WITH ANY OTHER PROGRAMS OR CIRCUITS), EVEN IF SUCH HOLDER OR OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Hm, looks a bit like the GNU public license. I fact it is my intention to make this book public available similar to the way the GNU public license does it for software.

# 2 The top level of a chip

# 2.1 How to get the correct data of a chip

In the old days the data of a chip was kept in a UNIX directory. To produce the masks you needed the GDS2 data. GDS2 mainly deals with geometries and some hierarchical information. Besides that it is a file similar to a tar file. To produce the GDS2 file you need a layout. The layout is usually in a design library. To get going you just needed the following informations:

- 1. The UNIX path to the library

- 2. The name of the top cell (usually the view layout)

- 3. The path where to place the GDS2 file

To check consistency of schematic and layout you just had to run an extract run and run an (This creates a netlist of the layout) LVS (layout versus schematic). The LVS compares if the netlist of the schematic and the netlist of the layout are equal. If both are equal you get a pass, if they differ you get an error listing. If the error listing holds more than only parameter errors you better forget about the GDS2 and start fixing.....

If the LVS is error free you could do a stream out and send the GDS2 file to the mask shop.

Typical naming convention was in the top level cell. It consisted of the chip name and a trailing version description such as A1 for first release, first metal or B2 for second release (all layer change) second metal version. To make things even more fool proof it was common to have a chip name written in metal on the layout and to name the GDS2 file in exactly the same way. (Something like U412B2.gds)

Note: Usually the stream out procedure uses view layout only! views such as layout1, layout2 etc for different versions of the layout are ignored! Never create different layouts of the same schematic with names differing from layout. GDS stream out will ignore them even if your design system shows them correctly!

# 2.1.1 Versioning tools

These simple days are over! Now we have versioning tools that can create a lot of more confusion. Within one database you may have dozens of versions of the schematic and the layout (and whatever view else you might have). Which schematic version is consistent with which layout version is only mapped by the tag! The person issuing the tag is fully responsible for the correctness! It may well be that there is a schematic version 1.52 that maps to a layout version 1.98 and you have almost no chance finding this out without a correct tag. It is no more the name of the top cell that is giving you the information. Even worse, now there may be a U412B2 layout version 1.3 that

is completely different from U412B2 layout version 1.32 although both are still named U412B2! It is the tag only telling you what you work on.

Tags are used in an inflationary way not only describing tape out versions but also all kinds of intermediate versions used for simulation etc.

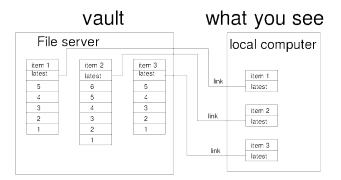

To order that mess it is mandatory to have some way of assigning which version of a block belongs to which top level. Unfortunately this usually is done in the population process. Population is the process of linking the data sitting in something called vault (Any relation Vault <-> Voldemort? The dark magician in Harry Potter? Who knows?). he vault is a big chunk of data that everybody hopes he will not have to debug. In this vault there are dozens of versions of each item (no matter if it is a schematic, symbol, layout, netlist, software, grandma's cookie recipe.....whatever). Populating means some software creates links between these files representing the items and your local directory.

In most cases default is simply linking the latest version found in the vault - no matter if it is consistent or not! (So on the top level schematic you might find buses with a different width than the module pins require. The linking software has no intelligence to see that.)

Figure 2.1: Population using the default "latest"

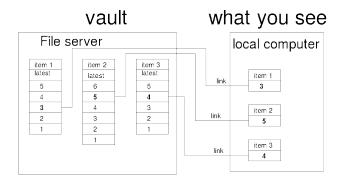

Alternatively the links can point to older versions. This makes sense if the latest version still is work in progress. For instance the layout corresponding to the latest schematic is not yet finished. Using such a work in progress version would lead to LVS (layout versus schematic test) and DRC (design rule check) errors in the top level data base.

Figure 2.2: Population of a tagged vault represents the versions item 1 ver. 3, item 2 ver. 5 and item 3 ver. 4 to the chip designer.

The configuration of the correct links is one of the most risky activities in the whole design process of a chip. One single wrong link can lead to a useless mask set. Therefore it is good engineering practice to create the tagged version, close the data base and repopulate using the automatic procedure that creates the links. Once this is done run DRC and LVS to verifify that at least there is no mayor disaster such as shorts or opens in the design.

This still does not guarantee full functionality! There could be versions of modules that have identical pins but still have different behavior. So these will not even be caught by DRC and LVS. To find out such issues the whole top level should also be resimulated before ordering the masks. For this reason project planning should provide some weeks between tape out and mask making.

**Getting started:** One of the first questions entering a project is how to start the population. Typically there is a script (usually a shell script) to be called. Something like

```

enter_project 'devicename'

```

This command should list all tagged versions and 'default'. 'default means populate the latest version. Every tagged version if selected should search a database describing which versions are to be linked. In very simple cases populating a tagged version could simply call some shell code holding many lines such as:

In -s /vault ... / module / view / version . / module / view

Not very elegant but working. More elegant would be a perl script (or whatever else is good in handling regular expressions) reading a data base.

Once this is done the chip designer should see a library at his local computer that corresponds the version selected. Unfortunately one of the best kept secrets in many design departments is where to find the list of module versions belonging to a specific database. So desperate chip designer frequently fuzz around simulating and redesigning the wrong module version. (I wish I could have 1% of the money burnt by working on the wrong version. I wouldn't need to write a book and would go climbing instead!)

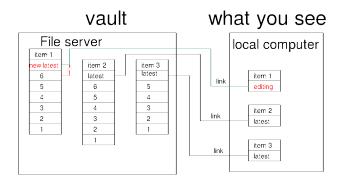

**Check out:** To edit data the data first has to be checked out. Checking out creates a copy of the version checked out (typically 'latest' will have a number only and there now is a new 'latest'.)

Figure 2.3: Editing under design sync. The green link is created new after checkout.

During editing revision 6 is kept but revision 7 is not yet assigned a version number. It can still be revoked by canceling the check out. The 'new latest version becomes a valid revision (that can no more be revoked) as soon as it is checked in.

**The DSS crash problem** Design sync stores who checked out data and from which server the checkout was done. If the session crashes while something was checked out and the same user starts a new session but gets a different server editing is no more possible. (Miller can't check out because the design is already checked out by Miller....). There are two possible solutions to fix the problem:

- 1. An administrator must fix the problem hacking the files directly inside the vault

- 2. Copy the design to a new name and edit the new design. In the design level above now the new design must be instantiated. The trace-ability of changes now is lost.

The same happens if you close the server connection while the CAD software is still running.

**Team blockage by design sync:** If a design (possibly by accident without intention) was checked out by one user nobody else can edit anymore. This happens frequently using for instance the Cadence mixed mode simulation environment. Before going into vacation check if there are any checkouts that you may have done unintentionally. If you block the team they can do nothing but let an administrator hack the vault or rename everything.

As a consequence working in a team it is required to check in much more often than there really are completed design steps. So most libraries hold about three times more checked in intermediate versions of a design than consistent design states. Version numbers of schematic, symbol and layout will run out of sync rapidly. Therefore it is necessary to tag versions. Tagging assigns the version numbers of different views to each other. (For instance a symbol ver. 3 could be associated with schematic ver. 20 and layout ver. 8 and be used in top level ver. 4....) A loss of these assignments makes a design almost useless even if the complete libraries still exist. (This is similar to the configuration of a big software project such as a complete operating system.)

**Risks of versioning:** The highest risk of versioning tools is to work on an outdated copy of a data base without being aware of it. Using DesSync GUI to check out parts of a data base can't be recommended at all!

Splitting a project into several databases will sooner or later lead to a crash because one database is checked out as current and in edit mode while you see outdated parts of the other data base (in read mode, not repopulated recently).

Imagine you see obsolete symbols coming from one data base while you are editing the schematics instantiating these symbols in the other data base. You will end up with broken connections at tape out! If you are lucky an LVS check will intercept this. If the LVS uses the same partial check out even the LVS won't find it and it depends on your luck which data eventually is used for GDS stream out. There is no automatic verification tool checking the correctness of your population!

Now since you are aware of the main risks, let's get going!

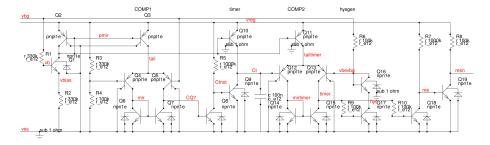

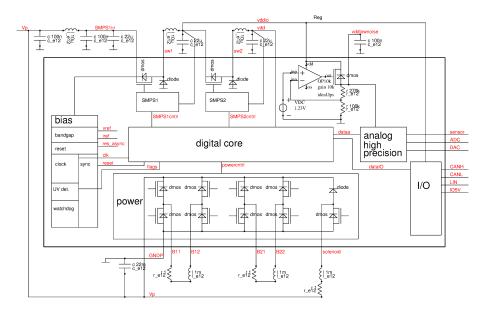

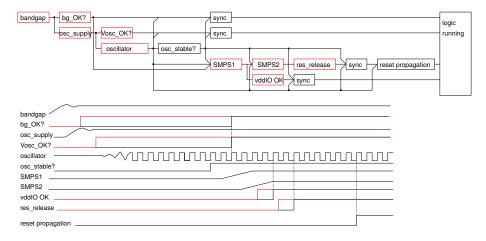

#### 2.2 System on a chip

SOC or system on a chip - the newest buzz word! Modern chips try to include more and more functions. Logic is cheap because it scales nicely with every new generation of technologies. So IC manufacturers try to add value plugging more and more logic into the chips. These chips require big teams to design them. Depending on the role of the team member everybody has a different perception of what a certain block does and what are the important interfaces.

An analog designer will regard a pin as something providing voltage and current with a certain impedance and signal swing. Some of them regard ground and supply as superconductive. The more experienced ones might even already have heard of pin inductance.

The system designer being more used to tools like Mathlab or compilers may already forget these unimportant details. He is more of a generalist. A pin is something providing a floating point number - and that's it!

The digital designer works with bits and bytes. Floating point MUST be avoided because it leads to very expensive arithmetic units. If any possible it all gets truncated to integer. (You can simulate a complete delta sigma converter in verilog. For the analog signal you just create a 32 bit bus and choose the LSB as  $10\mu V$ . Why fuzz with such strange concepts as floating point or voltages that just consume computation power?). Furthermore digital often has no power supply. This is SOP (somebody other's problem).

The project manager is in charge of dates and cost. Why should he worry about volts, amperes or data types? Since cost matters the project manager may have hired architects ,WEB designers or unemployed professors to

do the layout. Expertise I found in the layout teams can vary extremely from zero to Einstein's level! CAD software specialists neither care for physical properties (like voltage and current) nor for such primitive things